How To Perform Static Timing Analysis (STA) for Correct FPGA Operation

Static Timing Analysis (STA) is a cornerstone of FPGA design, ensuring that your digital circuit operates reliably within specified timing

Static Timing Analysis (STA) is a cornerstone of FPGA design, ensuring that your digital circuit operates reliably within specified timing

In the pursuit of performance and efficiency, embedded systems are increasingly embracing a heterogeneous architecture – a powerful combination of

FPGAs (Field-Programmable Gate Arrays) are highly regarded for their unparalleled flexibility in real-time processing. However, their full potential is realized

Block RAM (BRAM) is a cornerstone of FPGA design, offering high-speed, on-chip memory solutions crucial for efficient data handling. This

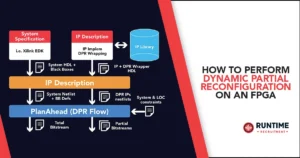

Dynamic Partial Reconfiguration (DPR) is an advanced FPGA technique that allows for the modification of specific FPGA blocks while the

Instruction Set Architectures (ISAs) are the fundamental blueprints defining how software interacts with hardware. Traditionally, these have been rigid, monolithic

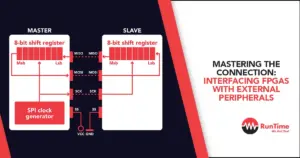

Field Programmable Gate Arrays (FPGAs) offer unparalleled flexibility in implementing digital logic. Their inherent configurability makes them ideal for building

As field engineers, we understand the critical role data integrity plays in FPGA-based communication systems. Even a single-bit error during

One of the most crucial challenges lies in extending the battery life of resource-constrained devices. These devices, often deployed in

Traditional storage solutions often struggle under the ever-increasing weight of information. For tech professionals, the ability to seamlessly scale data