FPGAs enable efficient and customizable hardware solutions. Optimizing routing and placement is crucial for better performance, lower power consumption, and improved resource utilization. This article covers practical approaches and best practices for optimizing FPGA routing and placement.

Understanding FPGA Routing and Placement

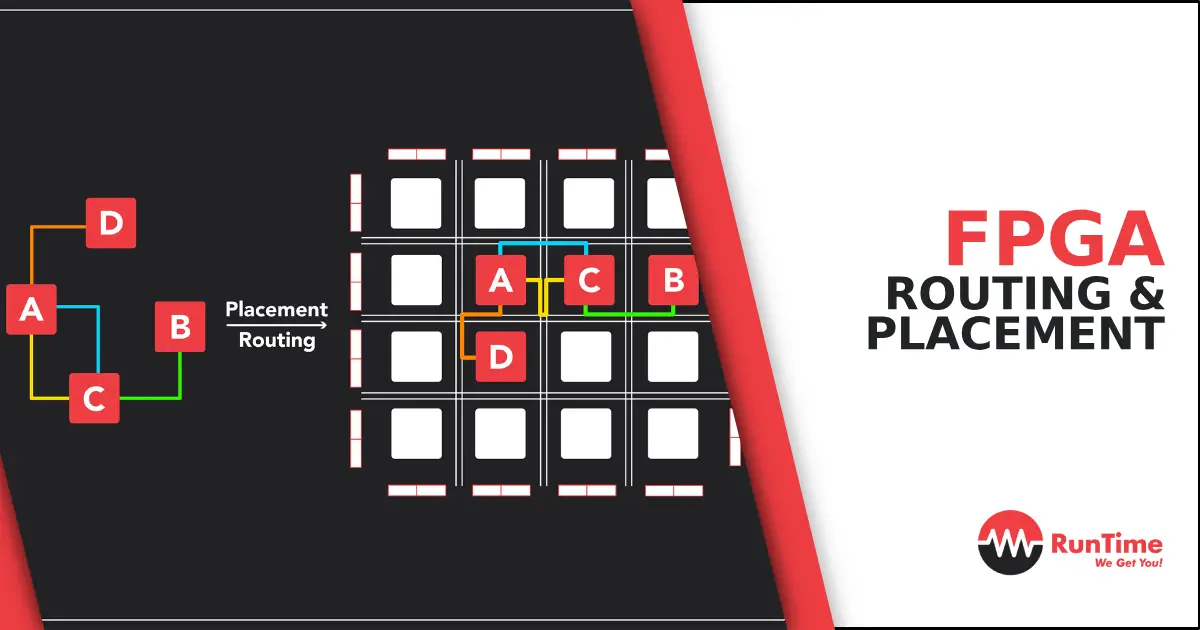

Before diving into optimization strategies, it is essential to thoroughly understand the key concepts of FPGA routing and placement. FPGA routing refers to the process of connecting logic elements through programmable interconnects, while placement involves positioning these logic elements on the FPGA’s configurable logic blocks (CLBs).

Several factors influence the effectiveness of FPGA routing and placement, with some of the most critical ones being:

- Device architecture: The specific FPGA architecture, which includes the arrangement of CLBs, interconnects, and other elements, plays a significant role in determining the optimal routing and placement strategy.

- Design constraints and objectives: The performance goals and constraints of the design, such as maximum operating frequency, power budget, and resource usage, directly impact the routing and placement decisions.

- Physical limitations and restrictions: Physical factors like the size of the FPGA, the number of available resources, and the routing capacity also affect the routing and placement process.

Optimizing FPGA routing and placement is not without its challenges, which must be addressed to achieve the desired performance, power, and resource utilization. Some of the most common challenges include:

- Timing closure: Ensuring that all timing constraints are met across the entire design is crucial for optimal performance. Meeting the timing requirements can be particularly challenging in large and complex designs, necessitating careful consideration of routing and placement strategies.

- Resource utilization: Efficiently using the available FPGA resources, such as logic elements, interconnects, and memory blocks, is critical for reducing costs and improving performance. A well-optimized design should maximize resource utilization without sacrificing performance or power efficiency.

- Power consumption: Reducing power consumption is a priority for many applications, especially those with strict power budgets or thermal constraints. Optimized routing and placement strategies should minimize power consumption while maintaining the required performance levels.

Strategies for FPGA Routing

Optimizing FPGA routing is crucial to achieving better performance, resource utilization, and power efficiency. In this section, we will discuss three major strategies for FPGA routing, which include top-down hierarchical design, adaptive routing algorithms, and utilizing FPGA-specific routing resources.

Top-down Hierarchical Design

A top-down hierarchical design approach is highly beneficial for optimizing FPGA routing. This methodology involves breaking down a complex design into smaller, more manageable blocks or submodules, which can be routed and optimized individually. By focusing on smaller design elements, engineers can significantly improve routing quality and efficiency while maintaining control over the overall design.

Some tips for effective top-down routing include:

- Identifying natural hierarchies and partitioning the design based on function, performance, or other criteria.

- Using modular design techniques to create reusable and scalable blocks.

- Applying consistent routing methodologies and constraints across all levels of the hierarchy.

- Performing iterative optimization and verification at each level to ensure optimal performance and resource utilization.

Adaptive Routing Algorithms

Adaptive routing algorithms are another powerful tool for optimizing FPGA routing. These algorithms dynamically adjust routing paths based on the current state of the FPGA resources, design constraints, and performance objectives. By continuously adapting to changing conditions, adaptive routing algorithms can effectively balance resource utilization, performance, and power consumption.

However, it is essential to consider the benefits and limitations of adaptive routing algorithms. While they can significantly improve routing quality and efficiency, they may also increase design complexity and require additional computational resources. As a result, engineers should carefully evaluate the trade-offs and select the most appropriate adaptive routing algorithm for their specific design requirements.

Utilizing FPGA-specific Routing Resources

Lastly, leveraging FPGA-specific routing resources is crucial for achieving optimal routing results. These resources, which may include dedicated routing channels, programmable interconnect points (PIPs), and specialized routing structures, can greatly enhance routing flexibility and efficiency.

Some best practices for using FPGA-specific routing resources include:

- Understanding the unique features and capabilities of the target FPGA architecture.

- Selecting the most appropriate routing resources based on design constraints and performance objectives.

- Employing specialized routing structures, such as clock networks and high-speed I/O interfaces, to optimize performance and power consumption.

- Regularly updating routing constraints and methodologies to take advantage of new FPGA features and improvements.

Strategies for FPGA Placement

Optimizing FPGA placement is equally important to routing for achieving high-performance and efficient designs. In this section, we will explore three main strategies for FPGA placement: logic partitioning and clustering, timing-driven placement, and utilizing FPGA-specific placement resources.

Logic Partitioning and Clustering

Effective FPGA placement begins with the strategic organization of the design’s logic elements. Logic partitioning and clustering involve grouping related logic elements based on functionality, performance requirements, or other criteria. This approach simplifies the design, promotes modularity, and enhances placement quality. Furthermore, logic partitioning and clustering can lead to improved timing closure, resource utilization, and power efficiency.

Techniques for effective logic partitioning and clustering include:

- Identifying natural hierarchies within the design and organizing logic elements accordingly.

- Employing functional clustering algorithms that group elements based on their connectivity and interdependence.

- Using FPGA-specific placement features, such as dedicated logic regions and configurable logic block (CLB) templates, to guide clustering decisions.

Timing-Driven Placement

Considering timing during the placement process is crucial for achieving optimal performance. Timing-driven placement algorithms analyze the design’s timing requirements and constraints, positioning logic elements in a manner that minimizes delays and enhances performance. By focusing on timing during placement, engineers can better address challenges related to timing closure and achieve more efficient designs.

Strategies for achieving better timing-driven placement include:

- Incorporating timing information into the placement process, either through constraint-driven placement or more advanced optimization techniques.

- Utilizing FPGA-specific features and tools that support timing-driven placement, such as timing-aware placement engines and dedicated clock routing resources.

- Iteratively refining the placement solution based on timing analysis results and adjusting placement constraints as needed.

Utilizing FPGA-Specific Placement Resources

Finally, leveraging FPGA-specific placement resources is essential for achieving optimal placement results. These resources may include dedicated logic regions, CLB templates, and other specialized placement features that enhance placement flexibility and efficiency.

Best practices for using FPGA-specific placement resources include:

- Understanding the unique features and capabilities of the target FPGA architecture and how they can be used to guide placement decisions.

- Selecting the most appropriate placement resources based on design constraints and performance objectives.

- Employing dedicated logic regions and other specialized placement features to optimize resource utilization, power consumption, and performance.

- Regularly updating placement constraints and methodologies to take advantage of new FPGA features and improvements.

Tools and Techniques for FPGA Routing and Placement Optimization

To achieve optimal FPGA routing and placement, engineers need access to a variety of specialized tools and techniques that cater to their specific design requirements. These tools and techniques offer invaluable support in optimizing routing and placement, enabling the development of high-performance and efficient FPGA designs.

There are numerous tools and techniques available for FPGA routing and placement optimization, each with its unique features and capabilities. Some popular tools include:

- Xilinx Vivado Design Suite

- Intel Quartus Prime Design Software

- Lattice Diamond Design Software

- Microsemi Libero SoC Design Suite

- Altera Design Flow

When selecting the appropriate tool, it is essential to consider factors such as the target FPGA architecture, design constraints, performance objectives, and compatibility with existing design workflows. A thorough comparison of popular FPGA routing and placement optimization tools can help engineers identify the most suitable option for their specific needs.

One crucial aspect of using these tools effectively is customizing them to meet specific design requirements. This customization may involve adjusting tool settings, modifying routing and placement constraints, or integrating custom algorithms and techniques tailored to the particular design. By thoroughly explaining and customizing these tools and techniques, engineers can obtain the best possible results for their FPGA routing and placement optimization efforts.

Conclusion

Optimizing FPGA routing and placement is instrumental in unlocking the full potential of Field-Programmable Gate Arrays. The importance of considering timing, resource utilization, and power consumption cannot be overstated. With the right tools and techniques, tailored to specific design requirements, engineers can navigate the challenges and achieve optimization goals.

As technology advances, continuous updates and customization of routing and placement methodologies will be crucial. The insights shared in this article aim to empower engineers in their pursuit of creating cutting-edge FPGA designs, ultimately contributing to the evolution of embedded industries.

Hire the Best Engineers with RunTime Recruitment

If you’re searching for highly skilled engineers worldwide, our expert team of engineers-turned-recruiters is here to help you. We offer in-depth knowledge of technical recruiting in the engineering industry to make the sourcing process much easier for you.

On the other hand, if you’re an engineer looking for new opportunities, RunTime Recruitment’s job site is the perfect place to find job vacancies.