Analog circuits are the unsung heroes, translating real-world phenomena into the digital language our microcontrollers understand. From sensor interfaces to power management units, their precise operation is paramount. Yet, unlike their digital counterparts, analog circuits are notoriously susceptible to variations – temperature drift, aging, manufacturing tolerances, and even subtle electromagnetic interference can nudge them off course, leading to performance degradation or outright failure.

Traditionally, monitoring and troubleshooting analog circuits have been a labor-intensive, post-production affair, often requiring expensive external test equipment and specialized expertise. But what if our analog circuits could tell us, proactively, when something is amiss? What if they could diagnose their own ailments, much like a sophisticated medical device monitors a patient’s vital signs?

Enter the fascinating and increasingly critical field of Self-Monitoring Analog Circuits, empowered by the implementation of Built-In Self-Test (BIST). This isn’t just about catching errors at the end of the production line; it’s about embedding intelligence directly into the analog domain, enabling continuous health checks, predictive maintenance, and ultimately, a new era of reliability and autonomy for embedded systems.

The Imperative for Self-Monitoring: Why BIST is No Longer a Luxury

For embedded engineers, the push for self-monitoring analog circuits stems from several compelling factors:

- Miniaturization and Complexity: Modern embedded systems are shrinking while their complexity skyrockets. Packing more analog functionality into smaller footprints makes external probing and debugging increasingly difficult, if not impossible.

- Reliability Demands: From medical implants to autonomous vehicles, the consequences of analog circuit failure can be catastrophic. Proactive fault detection and mitigation are essential for safety-critical applications.

- Cost Reduction: Post-production testing, field diagnostics, and warranty claims are significant cost drivers. BIST can dramatically reduce these expenses by identifying issues earlier and enabling more efficient in-situ repair or replacement.

- Predictive Maintenance: Moving beyond reactive repairs, BIST facilitates predictive maintenance strategies. By trending performance parameters, systems can anticipate failures before they occur, allowing for planned interventions and minimizing downtime.

- Autonomous Operation: For systems operating in remote or inaccessible environments (e.g., deep-sea sensors, satellite systems), continuous self-assessment is vital for sustained operation without human intervention.

- Supply Chain Vulnerability: As supply chains become more global and fragmented, ensuring the quality and authenticity of components is a growing concern. BIST can offer an additional layer of assurance regarding circuit integrity.

The Analog BIST Challenge: A Different Beast

While BIST has been a well-established practice in the digital world for decades, applying it to analog circuits presents a unique set of challenges:

- Continuous Nature: Digital signals are discrete (0 or 1), making fault detection relatively straightforward. Analog signals are continuous, requiring more sophisticated methods to characterize their behavior and identify deviations.

- Tolerance and Variation: Analog circuits are inherently susceptible to manufacturing variations and environmental factors. Defining “faulty” versus “acceptable” performance requires careful statistical analysis and understanding of design margins.

- Measurement Accuracy: On-chip measurements, especially with limited resources, must be sufficiently accurate to detect subtle anomalies without being overly sensitive to normal variations.

- Test Signal Generation: Generating precise analog test signals on-chip, particularly for complex waveforms or high frequencies, can consume significant area and power.

- Response Analysis: Interpreting the analog response to test signals and identifying specific fault conditions requires sophisticated signal processing and decision-making logic.

- Area and Power Overhead: Adding BIST circuitry inevitably consumes silicon area and power, which are often at a premium in embedded designs. A judicious balance must be struck between testability and resource constraints.

- Mixed-Signal Interaction: Many modern embedded systems feature tightly integrated mixed-signal circuits. BIST strategies must consider the interplay between analog and digital domains.

Core Principles and Techniques for Analog BIST

Despite the challenges, a variety of ingenious techniques have emerged to enable robust analog BIST. These generally fall into a few key categories:

1. Stimulus Generation (On-Chip Test Signal Generation)

- Simple Waveform Generators: For basic tests, on-chip oscillators (e.g., ring oscillators, relaxation oscillators) can generate square, sine, or triangular waves. Their frequency and amplitude can be controlled digitally.

- Programmable Signal Generators: More advanced designs might incorporate Digital-to-Analog Converters (DACs) driven by digital test patterns to produce arbitrary waveforms. This offers greater flexibility but with higher complexity and power consumption.

- Noise-Based Testing: Injecting controlled white noise and analyzing the circuit’s response in the frequency domain (e.g., using a built-in FFT engine) can reveal subtle non-linearities and parameter shifts.

- Parametric Excitation: Applying specific DC biases or pulsed signals to stress the circuit’s operating points can expose vulnerabilities not evident under normal operating conditions.

2. Response Measurement and Data Acquisition

- Analog-to-Digital Converters (ADCs): The most common method. An on-chip ADC converts the analog response to a digital stream for analysis. The choice of ADC (SAR, Delta-Sigma, etc.) depends on resolution, speed, and area constraints.

- Comparators: For simple go/no-go tests, comparators can check if an analog signal exceeds or falls below certain thresholds.

- Peak Detectors/RMS Converters: These can provide summarized information about the signal’s amplitude or power, reducing the amount of raw data that needs to be digitized.

- Frequency Counters/Period Measurement: For circuits whose performance is characterized by frequency (e.g., oscillators, filters), simple digital counters can measure the output frequency or period.

- Power/Current Monitoring: Integrating current sensors or voltage monitoring circuits can detect abnormal power consumption patterns, often indicative of short circuits, opens, or component degradation.

3. Data Processing and Decision Making (On-Chip Intelligence)

- Threshold Comparison: The simplest form of analysis, where measured values are compared against pre-defined upper and lower limits.

- Statistical Analysis: More sophisticated BIST systems might collect multiple readings and perform statistical analysis (e.g., mean, standard deviation) to track trends and detect gradual degradation.

- Signature Analysis: Analogous to digital signature analysis, the measured analog response can be compressed into a unique “signature” (e.g., using a cyclic redundancy check – CRC – or a checksum). Deviations from the golden signature indicate a fault.

- Machine Learning/AI: An emerging frontier. Small, optimized neural networks or other ML algorithms can be trained on a dataset of healthy and faulty circuit responses. These “on-chip brains” can then autonomously classify circuit health and even predict specific fault types. This is particularly powerful for complex, multi-parameter analog systems.

- Built-in Reference Generation: Some BIST schemes rely on an on-chip precision reference (voltage, current, or frequency) against which the circuit under test (CUT) can be compared. This reduces dependence on external, off-chip accuracy.

4. Test Scheduling and Control Logic

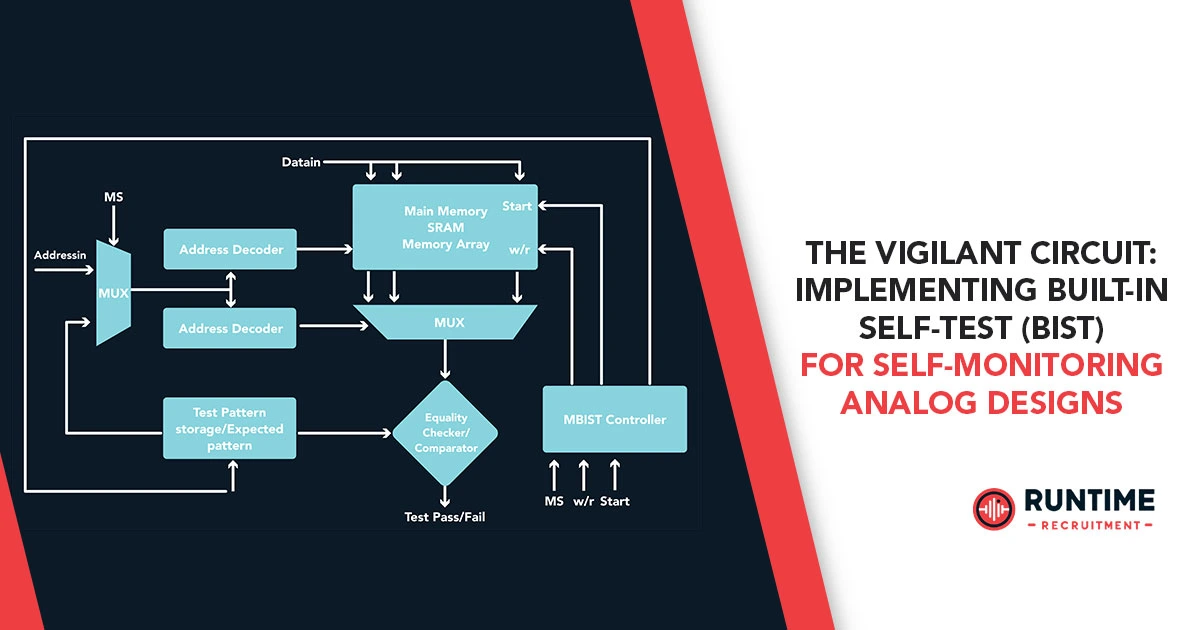

- State Machines: A digital state machine is often employed to orchestrate the BIST process, controlling stimulus generation, measurement cycles, and data acquisition.

- Scan Chains (Adapted for Analog): While traditionally digital, the concept of scanning through different test points can be adapted for analog using multiplexers and demultiplexers to route signals to a centralized measurement unit.

- Test Access Port (TAP) and JTAG Integration: For larger systems, the BIST controller can be integrated into a standard JTAG interface, allowing external control and data extraction for detailed analysis.

Case Studies and Practical Implementations (Illustrative Examples)

Let’s consider how Analog BIST principles are applied in real-world scenarios:

- Op-Amp Health Monitoring:

- Stimulus: On-chip DAC generates a precise sine wave input.

- Measurement: On-chip ADC digitizes the Op-Amp output.

- Analysis: Digital logic calculates gain, phase shift, and offset voltage. These parameters are compared against specifications. Degradation in gain or increasing offset can indicate aging or damage. For example, a significant drop in open-loop gain might suggest transistor degradation within the Op-Amp’s input stage.

- Power Management Unit (PMU) Self-Test:

- Stimulus: Internal digital control logic sets various output voltage and current load conditions for the DC-DC converter.

- Measurement: Integrated voltage and current sensors at the PMU output.

- Analysis: Digital logic monitors voltage regulation accuracy, current limit thresholds, and power efficiency under different loads. Deviations could indicate issues with internal feedback loops, power transistors, or control circuitry.

- MEMS Sensor Calibration and Health:

- Stimulus: For an accelerometer, an integrated actuator (e.g., electrostatic force) can apply known accelerations. For a pressure sensor, an integrated micro-pump could generate reference pressures.

- Measurement: The sensor’s analog output.

- Analysis: An on-chip microcontroller performs a multi-point calibration, storing coefficients. Over time, it can periodically re-test and compare current calibration values against stored ones. Drift beyond acceptable limits indicates sensor degradation or contamination.

- RF Front-End Self-Monitoring:

- Stimulus: An on-chip frequency synthesizer generates test tones.

- Measurement: Power detectors, spectrum analyzers (simplified, on-chip versions), or phase detectors monitor the output of LNAs, mixers, and filters.

- Analysis: Checking for gain compression, increased noise figure, or frequency shifts. This is particularly challenging due to high frequencies and stringent linearity requirements, often requiring advanced techniques like pseudo-random binary sequences (PRBS) and correlation for noise floor measurements.

Design Considerations and Best Practices for Embedded Engineers

Implementing effective Analog BIST requires careful planning and a holistic approach:

- Define Test Requirements Early: Don’t bolt BIST on as an afterthought. Integrate testability into the very first design specifications. What faults do you need to detect? What level of accuracy is required?

- Understand Fault Models: Unlike digital faults (stuck-at, bridging), analog faults are often parametric (e.g., resistance change, capacitance deviation, transistor transconductance shift). Develop specific test patterns to expose these.

- Minimize Test Overheads: Area, power, and performance penalties must be carefully weighed against the benefits of BIST. Clever multiplexing, shared resources, and re-purposing existing circuitry can help.

- Leverage Existing IP: Many foundries and IP vendors offer proven analog BIST blocks for common functions like ADCs, DACs, and references.

- Calibration and Characterization: Even with BIST, initial characterization and calibration are crucial. The BIST system needs a “golden reference” to compare against. This might involve an initial external calibration step or the use of on-chip, trimmed references.

- Robustness to PVT Variations: Ensure your BIST circuitry itself is robust to Process, Voltage, and Temperature (PVT) variations. The test results should reflect the CUT’s health, not the BIST circuit’s own sensitivity.

- Data Interpretation and Diagnostics: The BIST system should not just flag “fault,” but ideally provide diagnostic information about the nature and location of the fault, if possible. This is where advanced analytics or even on-chip ML can shine.

- Hierarchy and Modularity: For complex systems, breaking down BIST into smaller, modular blocks for individual analog sub-circuits can simplify design and debugging.

- Security Implications: In sensitive applications, consider potential security vulnerabilities introduced by BIST access ports. Ensure robust authentication and access control.

- Trade-offs: Granularity vs. Complexity: How fine-grained do your fault detections need to be? Detecting a general “Op-Amp failure” is easier than pinpointing which specific transistor failed. The required granularity will significantly impact BIST complexity.

The Future of Self-Monitoring Analog Circuits: Beyond BIST

The trajectory for self-monitoring analog circuits is exciting, extending beyond traditional BIST into areas like:

- Adaptive and Self-Healing Systems: Circuits that not only detect faults but can reconfigure themselves or compensate for degradation, perhaps by re-biasing components or routing signals around faulty sections.

- Predictive Maintenance with AI/ML: Even more sophisticated on-chip intelligence that can predict remaining useful life (RUL) and schedule preventative maintenance before critical failures occur. This involves continuous monitoring and sophisticated anomaly detection.

- IoT and Edge Computing Integration: Leveraging the continuous data from self-monitoring circuits to optimize performance, power consumption, and reliability in distributed IoT networks and edge devices.

- Security and Tamper Detection: Analog BIST can be used to detect physical tampering or cloning of chips by monitoring subtle changes in analog characteristics that would be indicative of unauthorized modifications.

- Reduced Design Cycles: By providing continuous feedback, BIST can shorten design cycles by allowing for more rapid prototyping and validation, identifying subtle issues much earlier.

Conclusion: Empowering the Next Generation of Embedded Systems

Self-monitoring analog circuits, driven by robust BIST implementations, are no longer a niche academic pursuit but an essential component of modern, reliable, and intelligent embedded systems. For embedded engineers, understanding the principles, techniques, and trade-offs involved in Analog BIST is becoming an increasingly valuable skill.

By imbuing our analog designs with the ability to observe, diagnose, and report on their own health, we are not only building more resilient and dependable products but also paving the way for truly autonomous systems that can operate with minimal human intervention, adapt to changing conditions, and provide unprecedented levels of insight into their own performance. The vigilant circuit is here, and it’s set to revolutionize how we approach reliability in the analog domain. Embrace the challenge, and unlock the immense potential of self-aware electronics.

Further Reading

For embedded engineers eager to delve deeper into the fascinating world of Analog BIST and self-monitoring analog circuits, consider exploring these resources:

- IEEE Transactions on Circuits and Systems

- International Solid-State Circuits Conference (ISSCC) Proceedings

- Design Automation Conference (DAC) Proceedings

Why Settle When You Can Excel?

Don’t let talent gaps delay your next big innovation. RunTime Recruitment is your strategic partner in securing the specialized embedded engineering professionals you need to thrive in a competitive landscape. We pride ourselves on efficiency, precision, and delivering candidates who truly make an impact from day one.

Ready to elevate your embedded engineering team? Partner with us today and experience the difference true expertise makes.