The pursuit of more intelligent, efficient, and autonomous edge devices is a perpetual frontier. From smart sensors and industrial IoT to wearable tech and autonomous vehicles, the demand for powerful AI capabilities at the very edge of the network is skyrocketing.

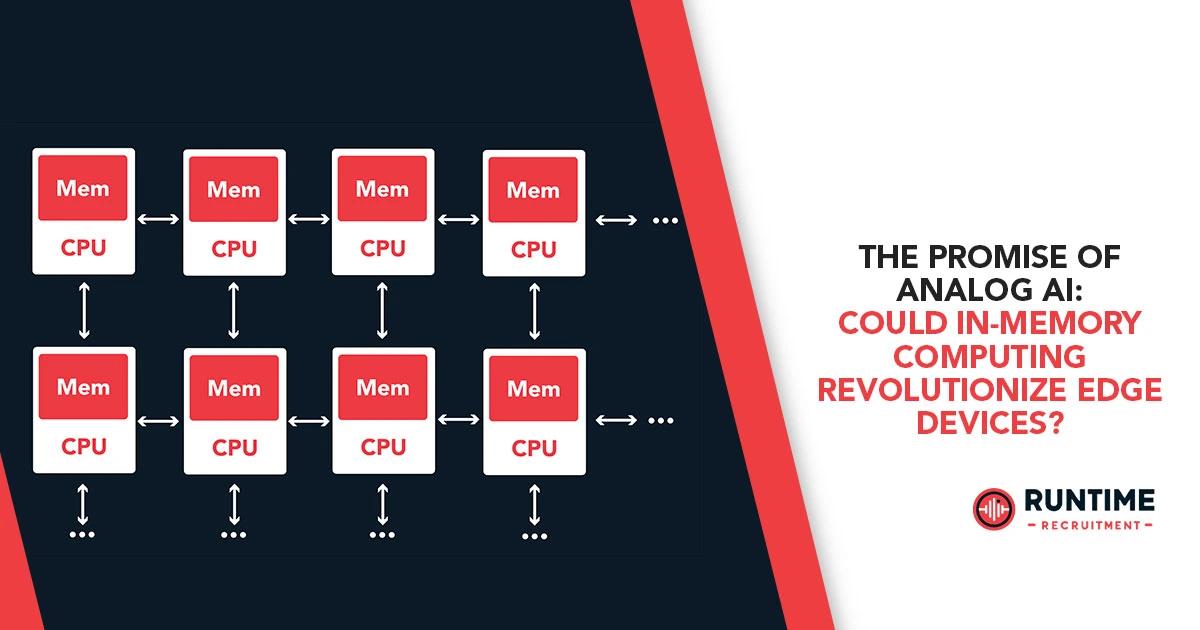

However, the traditional digital computing paradigm, with its fundamental separation of processing and memory (the Von Neumann bottleneck), is increasingly struggling to meet the stringent power, latency, and footprint requirements of sophisticated edge AI. Enter Analog AI and In-Memory Computing, a symbiotic pair that promises to break these barriers and usher in a new era of ultra-efficient edge intelligence.

The Digital Dilemma at the Edge

Digital computing, the bedrock of our modern technological landscape, relies on the constant shuttling of data between the processing unit (CPU/GPU/NPU) and memory. While incredibly versatile and precise, this data movement consumes significant energy and introduces latency, especially for the massive parallel operations inherent in Artificial Intelligence workloads like neural networks.

At the edge, these limitations are amplified. Embedded devices are often battery-powered, operate in thermally constrained environments, and demand real-time responsiveness. Running complex deep learning models on such devices leads to:

- High Power Consumption: Moving data back and forth from memory to processor is energy-intensive, drastically reducing battery life in mobile and IoT applications.

- Increased Latency: The constant data transfer creates bottlenecks, hindering real-time decision-making crucial for autonomous systems, industrial control, and medical devices.

- Large Footprint and Cost: The need for dedicated memory chips and complex interconnects adds to the physical size and bill of materials, making powerful edge AI economically unfeasible for many pervasive applications.

- Thermal Management Challenges: Higher power consumption directly translates to more heat generation, requiring larger and more complex cooling solutions, which are impractical for compact edge devices.

These challenges have led to a paradigm where much of the heavy AI lifting is offloaded to the cloud, undermining the very benefits of edge computing – privacy, low latency, and autonomy.

Analog AI: A Return to the Continuous

Analog computing, often seen as a relic of pre-digital electronics, is experiencing a renaissance in the context of AI. Unlike digital systems that represent information as discrete 0s and 1s, analog systems manipulate continuous physical quantities like voltage or current. This fundamental difference unlocks a powerful advantage for AI: computation can happen directly where the data resides.

Consider the core operation of a neural network: matrix-vector multiplication (MVM). In a digital system, this involves numerous fetch, multiply, and accumulate operations. In an analog system, these operations can be performed simultaneously and intrinsically through the physical properties of the memory elements themselves. For example, by applying voltages across an array of memristors (resistive memory devices), the currents flowing through them can represent the weighted sums, effectively performing MVM in a single, parallel step.

This “compute-in-place” capability is the essence of Analog AI and is precisely what gives it the potential to bypass the Von Neumann bottleneck.

In-Memory Computing: The Bridge to Edge Revolution

In-memory computing (IMC), also known as processing-in-memory (PIM) or compute-in-memory (CIM), is the architectural embodiment of Analog AI’s promise. It’s a design philosophy that merges processing elements directly within or very close to memory arrays. This dramatically reduces the need for data movement, leading to substantial gains in energy efficiency and speed.

While IMC can be implemented with digital processing units embedded within memory, the true disruptive potential for edge AI lies in Analog In-Memory Computing (AIMC). Here, the memory cells themselves (e.g., based on resistive random-access memory (RRAM), phase-change memory (PCM), or electrochemical random-access memory (ECRAM)) are not just storage elements but also active participants in the computation.

How AIMC works for AI:

- Storing Weights as Conductances: The synaptic weights of a neural network, which are typically stored digitally, are encoded as analog conductances (or resistances) within the memory devices.

- Parallel Multiplication: Input activations (voltages) are applied simultaneously across rows of these memory arrays.

- Current Summation: According to Ohm’s Law (I=V/R or I=V×G), the current flowing through each memory cell is proportional to the input voltage multiplied by its stored conductance (weight).

- Analog Accumulation: Kirchhoff’s Current Law ensures that the currents from individual cells along a column naturally sum up, representing the accumulated weighted sum – the core of neural network computation.

This massively parallel and inherent analog computation drastically reduces energy consumption and latency compared to their digital counterparts. Imagine a neural network layer executing in the time it takes for currents to propagate through a small array, rather than sequential digital operations.

Benefits for Embedded Engineers and Edge Devices

The implications of Analog In-Memory Computing for edge devices are profound, directly addressing the limitations faced by embedded engineers:

- Ultra-Low Power Consumption: By minimizing data movement and performing computations in the analog domain, AIMC chips can achieve orders of magnitude lower power consumption. This is a game-changer for battery-powered IoT devices, wearables, and remote sensors that need to operate for extended periods without recharging.

- Reduced Latency and Real-Time AI: The parallel, in-place computation eliminates the communication delays between processor and memory, enabling near-instantaneous inference. This is critical for applications demanding immediate responses, such as autonomous driving (object detection, path planning), industrial automation (defect detection, predictive maintenance), and medical diagnostics.

- Compact Form Factors: Integrating compute and memory reduces the need for separate chips and complex board designs, leading to smaller, lighter, and more cost-effective edge devices. This opens up possibilities for embedding AI into increasingly tiny form factors.

- Scalability for Larger Models at the Edge: While edge devices are resource-constrained, AIMC architectures can accommodate larger neural network models than traditional digital edge processors by efficiently handling the massive number of weights and computations. This could enable more sophisticated AI tasks to be performed locally. IBM Research, for instance, has demonstrated the feasibility of running transformer models, which are typically resource-heavy, on edge devices using phase-change memory for analog in-memory computing (IBM Research, 2025).

- Enhanced Privacy and Security: Processing data locally on the device, rather than sending it to the cloud, inherently enhances data privacy and reduces vulnerability to network-based attacks. This is particularly important for sensitive applications like healthcare and surveillance.

- Improved Robustness to Noise: While analog circuits are generally more susceptible to noise than digital ones, the inherent fault tolerance of neural networks can often compensate for minor inaccuracies introduced by analog computation. Furthermore, research is actively exploring techniques to make analog AI more robust.

Challenges and the Road Ahead

Despite its compelling promise, Analog In-Memory Computing is not without its challenges. Embedded engineers considering this technology need to be aware of:

- Precision and Accuracy: Analog computations inherently have lower precision than digital ones. While neural networks can be surprisingly resilient to this, developing robust training techniques (“hardware-aware training”) and hybrid analog-digital architectures that combine the efficiency of analog with the precision of digital is crucial.

- Non-Idealities and Variability: Real-world analog memory devices exhibit non-ideal characteristics and device-to-device variability, which can affect performance. Mitigating these effects through circuit design, calibration, and algorithmic approaches is an active area of research.

- Programming and Toolchains: Developing efficient programming models, compilers, and software toolchains that can effectively map AI models onto novel AIMC hardware architectures is a significant undertaking. This requires a shift from traditional software development paradigms.

- Manufacturing Scalability: Scaling the fabrication of high-density, reliable analog memory arrays with embedded compute capabilities to mass production levels presents engineering and manufacturing hurdles.

- Retraining and Adaptability: While AIMC excels at inference, efficient on-device training or continuous learning remains a more complex challenge dueishing to the complexity of updating analog weights. Hybrid solutions are likely to prevail, where training occurs in the cloud and inference at the edge, or where fine-tuning happens on the device.

Leading research institutions and companies are investing heavily in overcoming these challenges. IBM Research has been a pioneer in this space, showcasing their work on scalable hardware with 3D analog in-memory architecture for large models and demonstrating how phase-change memory can bring transformer models to the edge efficiently (IBM Research, 2025). Other research explores hybrid analog-digital neural network processors combining the parallel processing of analog memory with the precision of digital computation (SAS Publishers, 2025).

The Future of Edge AI: A Hybrid Landscape

The future of edge AI will likely be a hybrid landscape, where Analog In-Memory Computing complements and integrates with existing digital architectures. For highly specialized, power-sensitive inference tasks, AIMC will provide unmatched efficiency. For tasks requiring extreme precision or flexibility, digital accelerators will continue to play a vital role.

Embedded engineers will need to embrace a multidisciplinary approach, understanding both the intricacies of analog circuit design and the demands of machine learning algorithms. The development of sophisticated co-design tools that allow for seamless mapping of AI models onto heterogenous analog-digital hardware will be paramount.

Imagine a world where:

- Your smartwatch can perform complex health diagnostics with AI on-device, extending battery life from days to weeks.

- Autonomous vehicles make instantaneous, robust decisions without relying on constant cloud connectivity, enhancing safety and reliability.

- Industrial sensors identify subtle machinery anomalies in real-time, preventing costly breakdowns and optimizing production.

- Smart home devices offer truly personalized and responsive experiences, processing your preferences and commands locally and privately.

Analog AI, powered by the revolution of in-memory computing, is not just a theoretical concept; it is rapidly moving from the lab to practical implementation. For embedded engineers, staying abreast of these developments is not merely an academic exercise, but a necessity for shaping the next generation of intelligent, efficient, and pervasive edge devices. The promise is clear: the future of AI at the edge is analog, and it’s computing right where the data lives.

For Further Reading:

- IBM Research. (2025). How analog in-memory computing could power the AI models of tomorrow. Accessed July 16, 2025, from IBM Research Blog

- SAS Publishers. (2025). Hybrid Analog-Digital Neural Network Processor for Efficient AI Computing. Accessed July 16, 2025, from SAS Publishers Journal

- Milvus. (n.d.). What are the challenges of implementing edge AI? Accessed July 16, 2025, from Milvus AI Quick Reference

- Edirisooriya, M. (2024). The Analog Future of AI: How Small, Efficient LLMs Could Transform Everyday Technology. Accessed July 16, 2025, from Medium

Stop Searching, Start Innovating: Unlock Top Embedded Engineering Talent

Is your team ready to stop searching and start innovating? Partner with RunTime Recruitment today and secure the specialized embedded engineering professionals you need to thrive.

Contact us today and let us help you find the right fit for your company!