The embedded systems landscape is a complex tapestry woven from countless threads of Intellectual Property (IP). From microcontrollers and DSPs to communication interfaces and specialized accelerators, third-party IP cores are the bedrock of modern system-on-chip (SoC) design, enabling rapid development cycles and immense cost savings. However, this indispensable reliance on external IP introduces a critical vulnerability: the potential for malicious hardware to be stealthily embedded within these “trusted” components. For embedded engineers, understanding, identifying, and mitigating this insidious threat is no longer an academic exercise but a pressing imperative in safeguarding the integrity and security of critical systems.

The Expanding Attack Surface: Why Third-Party IP Cores are Prime Targets

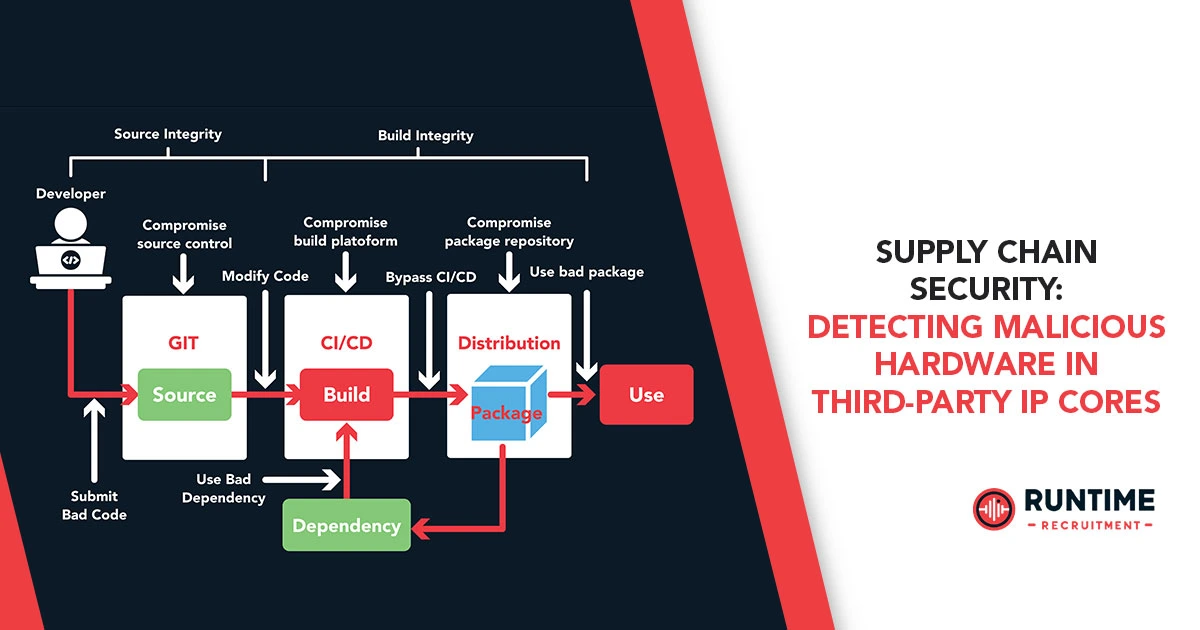

The globalization of the semiconductor supply chain has created a fertile ground for hardware-level attacks. Design houses, IP vendors, fabrication foundries, and assembly plants are often geographically dispersed and operate under varying security standards. This distributed model, while economically efficient, significantly expands the attack surface, making it challenging to ensure the trustworthiness of every component at every stage.

Hardware Trojans (HTs) are the most prominent form of malicious hardware. Unlike software vulnerabilities that can often be patched, HTs are physical modifications to the circuit design, embedded at various stages, from initial design (RTL), to gate-level netlists, and even during fabrication. Their stealthy nature makes them incredibly difficult to detect, as they are often designed to remain dormant until triggered by specific, rare conditions. Once activated, an HT can unleash a range of devastating payloads:

- Information Leakage: Exfiltrating sensitive data, cryptographic keys, or proprietary algorithms.

- Denial of Service (DoS): Causing system malfunctions, crashes, or complete operational halts.

- Functionality Alteration: Subtly changing the intended behavior of the system, leading to incorrect calculations, bypassed security checks, or unauthorized access.

- Performance Degradation: Introducing delays or reducing throughput, potentially impacting real-time critical applications.

- Side-Channel Attacks: Embedding sensors that leak information through power consumption, electromagnetic emissions, or timing variations, even if the primary functionality remains intact.

The integration of third-party IP cores exacerbates this threat. When an organization integrates an IP core, especially a “hard” IP (a fully laid out physical manifestation), they are essentially incorporating a black box. The inner workings are often obscured by proprietary concerns, making thorough verification a formidable challenge. A malicious actor, whether an disgruntled insider at an IP vendor or a state-sponsored entity, could implant an HT during the IP core’s design or even in the EDA tools used to process it.

The Elusive Nature of Hardware Trojans: Why Traditional Methods Fall Short

Traditional verification methodologies, while robust for functional correctness, are largely ill-equipped to detect sophisticated hardware Trojans. Functional testing, for instance, focuses on ensuring the IP performs its advertised functions. HTs, by design, are often carefully crafted to maintain nominal functionality under most operating conditions, only activating under very specific, often rare, trigger events. This makes them incredibly difficult to unearth through standard test vectors.

Similarly, formal verification, while powerful for proving the correctness of a design against a specification, struggles with the “unknown unknown” – the malicious logic that is intentionally undocumented and designed to evade standard property checks. Reverse engineering, though conceptually appealing, is often impractical for complex modern IP cores due to their sheer scale and the proprietary nature of their design. Furthermore, even if reverse engineering is feasible, identifying a subtle, intentionally hidden malicious circuit amidst millions of gates is a Herculean task.

A Multi-Faceted Approach: Strategies for Detecting Malicious Hardware

Detecting malicious hardware in third-party IP cores requires a comprehensive, multi-layered approach that goes beyond traditional verification. It necessitates a blend of design-time vigilance, advanced analysis techniques, and continuous monitoring.

1. Pre-Silicon Verification and Analysis

The earlier a Trojan is detected, the less costly and impactful it will be. Therefore, a significant focus must be placed on pre-silicon verification.

- Formal Verification for Security Properties: While general formal verification may miss HTs, applying formal methods specifically to security-critical properties can be more effective. This involves defining and formally verifying the absence of undesirable behaviors or the strict adherence to security protocols within the IP. For instance, ensuring that a cryptographic IP core strictly adheres to its specified cryptographic algorithm and does not contain any unintended side channels or backdoor mechanisms. Techniques like property checking, model checking, and equivalence checking can be employed to compare the IP against a trusted golden model or a set of security invariants.

- Structural Analysis and Anomaly Detection: This involves a deeper dive into the IP’s internal structure beyond its functional specification.

- Gate-Level Netlist Analysis: Analyzing the synthesized gate-level netlist for unusual structures, redundant logic, or connections that don’t seem to serve a legitimate purpose. Attackers often utilize unused or “dead” spaces in the layout for HT insertion. Techniques like filling these gaps with dummy logic can make insertion more difficult.

- Control Flow and Data Flow Analysis: Examining how data and control signals propagate through the IP. Any deviation from expected paths or the presence of hidden control logic could indicate an HT.

- Design Metric Anomaly Detection: Monitoring various design metrics (e.g., gate count, area, power consumption, timing paths) and comparing them against historical data or expected ranges for similar IP cores. Significant anomalies could signal the presence of extra, unauthorized logic. Machine learning algorithms are increasingly being used to establish baselines and identify subtle deviations.

- Code Coverage and Redundancy Analysis: Malicious logic often remains dormant and is triggered by rare events. Analyzing code coverage during simulation can help identify unused or rarely exercised portions of the design, which could potentially house an HT. Similarly, identifying and removing redundant circuitry can reduce the space available for HT insertion and simplify analysis.

- Hardware/Software Co-Verification: For IP cores with significant software interaction (e.g., processors), co-verification can be crucial. This involves running software alongside the hardware model and observing their combined behavior, looking for unexpected interactions or data leakage.

- Trusted IP Core Sourcing and Vetting: This is a foundational step. Establish rigorous procurement processes for third-party IP.

- Vendor Due Diligence: Thoroughly vet IP vendors, assessing their security practices, reputation, and supply chain controls. Require evidence of their internal security audits and certifications.

- Secure IP Delivery: Insist on secure delivery mechanisms for IP, including encryption and integrity checks, to prevent tampering during transit.

- Attestation and Provenance: Explore methods for IP attestation, which could provide cryptographic proof of the IP’s origin and integrity.

2. Post-Silicon Detection Techniques

Once the silicon is fabricated, detection becomes even more challenging, but not impossible.

- Side-Channel Analysis (SCA): HTs, even when dormant, can subtly alter the physical characteristics of a chip. SCA techniques exploit these unintended information leakages.

- Power Analysis: Measuring fluctuations in power consumption during operation. An HT, when triggered or even just existing, might cause minute deviations in power draw that can be detected. Differential power analysis (DPA) can be particularly effective in identifying subtle changes.

- Electromagnetic (EM) Analysis: Similar to power analysis, HTs can emit unique electromagnetic signatures.

- Thermal Analysis: Malicious logic might generate localized heat anomalies.

- Timing Analysis: HTs can introduce small, often intentional, delays in critical paths. High-resolution timing measurements can sometimes reveal these discrepancies. Shadow registers and delay measurement techniques can assist here.

- Runtime Monitoring and Anomaly Detection: Even after deployment, continuous monitoring can help identify activated HTs.

- On-Chip Sensors: Integrating hardware sensors within the SoC to monitor various parameters (e.g., voltage, temperature, clock frequency, critical signal integrity) in real-time. Deviations from established baselines could trigger an alert.

- Performance Monitoring Counters (PMCs): Leveraging existing PMCs in processors to detect unusual instruction sequences, cache misses, or power consumption patterns that might indicate an HT’s activity.

- Behavioral Anomaly Detection: Employing machine learning to profile the “normal” behavior of the embedded system and detect statistically significant deviations. This could include analyzing network traffic, I/O patterns, and CPU utilization.

- Non-Destructive and Semi-Destructive Reverse Engineering: For high-assurance applications, some level of reverse engineering might be considered post-fabrication.

- X-ray Tomography and Scanning Electron Microscopy (SEM): These techniques can provide detailed images of the chip’s internal layers, potentially revealing unexpected structures or modifications.

- Focused Ion Beam (FIB) Circuit Edit: While primarily a debug technique, FIB can be used to isolate and analyze suspicious regions of a chip.

3. Design-for-Security (DfS) and Trustworthiness

Beyond detection, proactively designing for security can significantly reduce the risk of HTs.

- Secure IP Core Design Best Practices: Encouraging IP vendors to adopt secure design principles, including:

- Minimalism: Designing IP with only the necessary functionality to reduce the attack surface.

- Isolation and Partitioning: Architecting the SoC to isolate critical IP cores, limiting the impact of a compromised component.

- Redundancy and Diversity: Implementing redundant IP cores from different vendors or using diverse design methodologies to reduce common mode failures and HT susceptibility.

- Obfuscation and Logic Locking: Techniques that make it harder for attackers to understand and modify the design. However, these can also complicate legitimate verification.

- Hardware Root of Trust (HRoT): Establishing a secure foundation for the system’s operation. An HRoT, typically a small, immutable piece of hardware, can verify the integrity of other hardware and software components during boot-up and runtime, including IP cores.

- Physical Unclonable Functions (PUFs): Leveraging inherent, unique manufacturing variations in silicon to create device-specific identities and cryptographic keys, making it harder for attackers to clone or tamper with devices. PUFs can be integrated into IP cores to enhance their trustworthiness.

The Road Ahead: Emerging Trends and Challenges

The battle against malicious hardware is a continuous arms race. Emerging trends and technologies are shaping the future of HT detection:

- Artificial Intelligence and Machine Learning: AI/ML will play an increasingly vital role in anomaly detection, particularly for identifying subtle side-channel leakages or behavioral deviations. This includes training models on known HT signatures and developing unsupervised learning techniques to detect novel attacks.

- Quantum Computing Threats: While still nascent, the advent of quantum computing poses a long-term threat to current cryptographic primitives. Embedded engineers must begin to consider quantum-resistant cryptographic IP cores.

- Formal Methods Advancements: Research continues into more sophisticated formal verification techniques capable of addressing the challenges of HT detection in complex, heterogeneous SoCs.

- Collaborative Security Frameworks: Greater collaboration between IP vendors, EDA tool providers, and system integrators is crucial to share threat intelligence, develop common security standards, and establish trusted supply chain partnerships.

- Blockchain for Supply Chain Transparency: Exploring the use of blockchain technology to create immutable records of IP core provenance and modifications throughout the supply chain.

Conclusion

The pervasive integration of third-party IP cores into embedded systems has brought immense benefits, but it has also introduced a profound security challenge: the risk of malicious hardware. Hardware Trojans, with their stealthy insertion and dormant nature, represent a formidable adversary. For embedded engineers, the era of assuming implicit trust in IP cores is over.

A proactive and multi-faceted approach is paramount. This involves not only employing advanced pre-silicon and post-silicon detection techniques like formal verification for security properties, structural analysis, and side-channel analysis, but also embracing a holistic “Design-for-Security” mindset. By rigorously vetting IP vendors, implementing robust security architectures, and continuously monitoring system behavior, embedded engineers can significantly bolster the resilience of their designs against the silent saboteurs lurking within the hardware supply chain. The future of embedded systems security hinges on our collective ability to establish and maintain trust in every transistor, gate, and IP core that forms the foundation of our digital world.