In the realm of advancing technology, Field-Programmable Gate Arrays (FPGAs) have emerged as key players in expediting hardware development. FPGA Intellectual Property (IP) cores offer pre-designed functional units seamlessly integrating into FPGA designs, streamlining the development process. This comprehensive guide delves into the intricacies of selecting, integrating, and customizing IP cores to align with specific project needs.

Explore the nuances of choosing the ideal IP core, implementing best integration practices, and optimizing core performance through customization. Whether you’re an experienced FPGA developer or new to the field, mastering the art of leveraging FPGA IP cores is essential for boosting productivity and achieving project success. Join us on this journey as we unravel the complexities of effectively utilizing FPGA IP cores to unlock the full potential of FPGA-based projects.

What are FPGA IP Cores?

Definition and Functionality:

Introduction to FPGA IP Cores

FPGA IP Cores are essential components in the field of Field-Programmable Gate Arrays (FPGAs). They are pre-designed blocks of code that offer a way to efficiently create FPGA designs. These cores encapsulate complex functionalities and are used to expedite the development process of FPGA-based projects. By integrating these IP cores, designers can focus more on the higher-level aspects of their designs rather than reinventing the wheel with every project.

Types of FPGA IP Cores:

Soft Cores

Soft cores are implemented using a hardware description language (HDL) and configured through the FPGA’s programming interface. They are flexible and easily customizable to suit specific project requirements. Soft cores are particularly useful in scenarios where the design needs to be altered frequently or when rapid prototyping is essential.

Hard Cores

In contrast, hard cores are firm, pre-designed blocks that are already embedded in the FPGA’s architecture during manufacturing. These cores offer high performance and are optimized for specific functions. Hard cores are beneficial when stringent timing requirements or high throughput capabilities are crucial for the design. They provide predictability and reliability in operation due to their dedicated hardware implementation.

Differences between Soft Cores and Hard Cores

The primary distinction between soft cores and hard cores lies in their configurability and implementation. Soft cores offer flexibility and ease of customization at the cost of performance, whereas hard cores prioritize performance and reliability at the expense of flexibility. Designers must weigh these factors carefully based on the project’s requirements and constraints.

Use Cases and Examples of Soft Cores and Hard Cores in FPGA Designs

Soft cores find applications in diverse fields such as signal processing, communication protocols, and encryption algorithms. They are prevalent in projects where adaptability and iterative development are paramount. On the other hand, hard cores excel in tasks like high-speed data processing, memory interfacing, and complex mathematical computations. Industries such as aerospace, telecommunications, and automotive rely on hard cores for their robust and optimized performance.

By leveraging a combination of soft cores and hard cores, FPGA designers can strike a balance between flexibility and performance, ultimately leading to efficient and effective FPGA designs.

Section: Choosing the Right IP Core

Choosing the right IP core for your project is a crucial decision that can impact the overall success and efficiency of your design. It involves evaluating various factors and considerations to ensure that the selected IP core aligns with your project requirements and goals. Let’s delve into the key points to consider when selecting an IP core:.

Factors to Evaluate for Selection:

- Functionality: Ensuring the IP core’s functionality aligns with the specific requirements of your project is paramount. Evaluate if the core provides the necessary features and capabilities to meet your design goals.

- Performance Metrics: Assess the performance metrics of the IP core, such as speed, latency, and throughput. It’s essential to choose a core that can efficiently handle the computational tasks required by your project.

- Area and Power Optimization: Consider the area and power consumption of the IP core. Opt for a core that optimizes resource utilization and energy efficiency in your design without compromising performance.

- Compatibility Check: Verify the compatibility of the IP core with your existing design tools, software, and hardware platforms. Compatibility issues can lead to integration challenges, so ensure seamless integration with your current setup.

Key Considerations in IP Core Selection:

- Quality and Reliability: Opt for IP cores from reputable providers known for their high-quality and reliable solutions. Choosing a trusted provider minimizes risks and ensures the reliability of the core in your project.

- Support and Documentation: Look for IP cores that offer comprehensive documentation, technical support, and maintenance services. Access to reliable support can greatly aid you throughout the design process and troubleshooting stages.

- Cost Evaluation: Evaluate the total cost of acquiring and integrating the IP core. Consider both upfront expenses and long-term maintenance costs to make an informed decision that aligns with your budget.

- Customization Options: Assess the flexibility and customization options provided by the IP core. Customization capabilities allow you to tailor the core to meet the specific requirements of your project effectively.

By meticulously evaluating these factors and considerations, you can confidently choose the right IP core for your project, ensuring a robust foundation for a successful design implementation.

Integrating FPGA IP Cores

Integrating FPGA IP cores is a critical aspect of designing complex digital systems. In this section, we will explore various effective methods used for integrating FPGA IP cores. From the utilization of vendor-specific tools like Xilinx Vivado and Intel Quartus to manual integration techniques involving HDL coding, we will delve into the details of each method. Understanding the strengths and limitations of these integration approaches is essential for achieving optimal performance and efficiency in FPGA-based designs.

Addressing Integration Challenges in FPGA Designs

Integrating FPGA IP cores presents a unique set of challenges that designers must overcome to ensure project success. Compatibility issues between IP cores, resource constraints such as limited hardware resources or timing constraints, and design complexity are common challenges faced during the integration process. To address these challenges effectively, designers need to adopt strategies like careful IP core selection, thorough simulation and verification procedures, and proper resource allocation.

Moreover, designers should also consider factors like power consumption, signal integrity, and design scalability when integrating FPGA IP cores. By incorporating best practices such as modular design methodologies and reuse of proven IP blocks, designers can streamline the integration process and enhance overall design reliability.

Integrating FPGA IP cores requires a comprehensive understanding of the available integration methods and the ability to tackle integration challenges proactively. By implementing a systematic approach that emphasizes thorough planning, rigorous testing, and continuous optimization, designers can achieve seamless integration of FPGA IP cores and deliver high-performance digital systems.

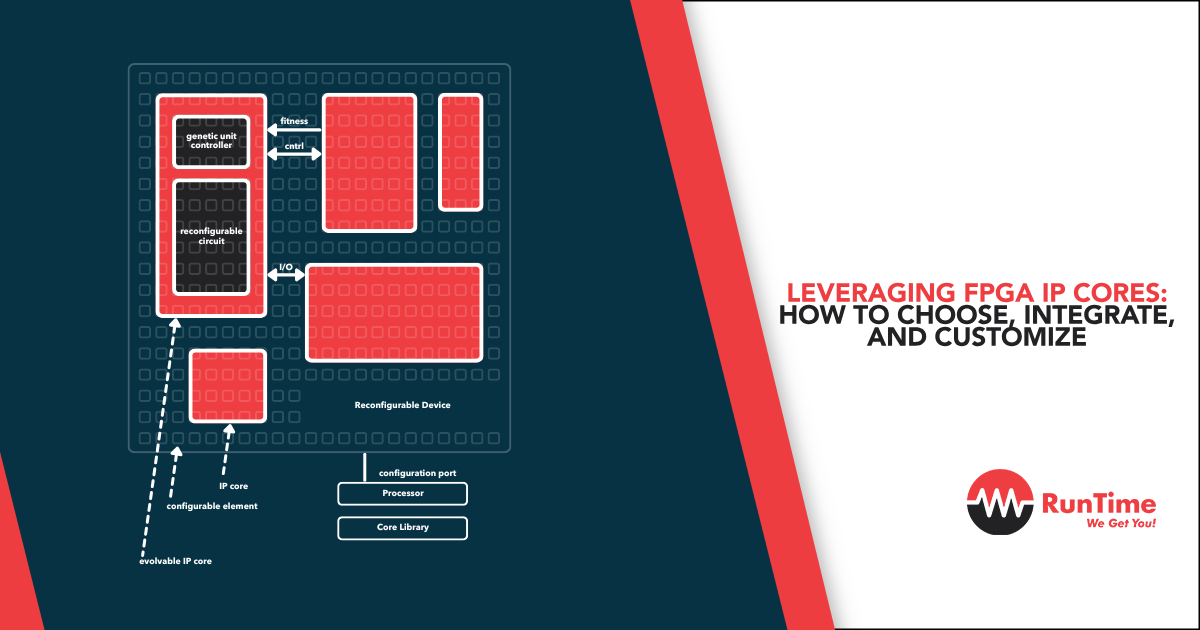

Advanced Integration Techniques

Beyond the fundamental methods of integrating FPGA IP cores, advanced techniques can further optimize the design process. Exploring concepts like partial reconfiguration, dynamic reconfiguration, and IP core pipelining can lead to enhanced flexibility, performance, and resource utilization in FPGA designs. These advanced techniques empower designers to adapt to changing requirements, maximize hardware utilization, and improve overall system efficiency.

Future Trends in FPGA IP Core Integration

The field of FPGA IP core integration is constantly evolving, driven by technological advancements and industry demands. Emerging trends such as increased focus on security and functional safety, the integration of artificial intelligence accelerators, and the rise of open-source IP cores are shaping the future of FPGA design. Designers must stay informed about these trends to leverage the latest innovations and stay competitive in the rapidly changing landscape of FPGA development.

By embracing innovation, staying updated on industry trends, and continuously refining integration methodologies, designers can push the boundaries of FPGA-based system design and unlock new possibilities for creating cutting-edge digital solutions.

Customizing IP Cores

Advantages of Customization

In the realm of integrated circuits (ICs), Intellectual Property (IP) cores play a crucial role as pre-designed building blocks that are fundamental for the creation of intricate systems. Customizing these IP cores offers a myriad of benefits to designers and engineers, empowering them to tailor these cores to meet specific project requirements. This customization enables the achievement of optimized performance, reduced resource utilization, and enhanced functionality, ultimately leading to the development of cutting-edge solutions. Dive deeper into this section to explore the multitude of advantages that come with customizing IP cores.

Guidelines for Effective Customization

While the idea of customizing IP cores may be alluring, it is paramount to approach this process with a strategic mindset. Without well-defined guidelines, customization endeavors can result in inefficiencies and obstacles. This segment of the blog will not only discuss the benefits of customization but also provide essential guidelines for effectively customizing IP cores. From comprehending design constraints and system requirements to ensuring seamless integration with existing technologies, these guidelines are designed to streamline the customization process, fostering innovation and ensuring successful outcomes in every project. Embrace the power of customization and unlock the full potential of IP cores with these insightful guidelines.

Importance of IP Core Customization

Customizing IP cores goes beyond mere modification; it is a strategic approach that can significantly impact the success of a project. By tailoring these cores to specific requirements, designers can achieve a level of optimization that is otherwise unattainable. This level of customization allows for enhanced performance, reduced power consumption, and improved compatibility within the larger system architecture. Moreover, customizing IP cores facilitates the incorporation of proprietary algorithms or functionalities, giving companies a competitive edge in their respective industries.

Streamlining Development Processes

One of the key advantages of customizing IP cores is the ability to streamline development processes. By starting with pre-designed building blocks, engineers can focus their efforts on the unique aspects of their projects rather than reinventing the wheel. This not only accelerates time-to-market but also ensures a more efficient use of resources. Furthermore, by adhering to established guidelines and best practices in customization, developers can avoid common pitfalls and design errors, leading to a more robust and reliable end product.

Ensuring Compatibility and Scalability

Effective customization of IP cores involves not only meeting current project requirements but also considering future scalability and compatibility. By carefully designing and customizing these cores, engineers can future-proof their designs, making them more adaptable to evolving technological landscapes. This forward-thinking approach ensures that projects remain relevant and competitive over extended periods, reducing the need for frequent redesigns or costly system overhauls. By following the guidelines for effective customization, designers can build a strong foundation for scalable and compatible systems that can grow and evolve alongside technological advancements.

Collaborative Customization Efforts

The process of customizing IP cores often involves collaboration among various stakeholders, including hardware and software engineers, system architects, and project managers. By fostering a collaborative environment where insights and expertise are shared, teams can leverage collective knowledge to produce superior customizations that align with project goals and requirements. Effective communication and coordination among team members can streamline customization efforts, reduce misunderstandings, and ensure that the final product meets or exceeds expectations. Embracing a collaborative approach to customization not only enhances the quality of the end product but also cultivates a culture of innovation and excellence within the organization.

Customizing IP cores is not merely a technical exercise but a strategic endeavor that can yield significant benefits for projects of all scales. By understanding the advantages of customization, following established guidelines, and embracing a collaborative approach, designers and engineers can unlock the full potential of IP cores and create solutions that are optimized, efficient, and future-ready.

As technology continues to advance at a rapid pace, the ability to customize IP cores effectively will be a key differentiator for companies seeking to innovate and stay ahead in the competitive landscape. Start your customization journey today and discover the endless possibilities that come with tailoring IP cores to fit your project’s unique requirements.

Optimizing IP Core Performance

Enhancing IP Core Performance

Optimizing IP core performance is crucial for achieving high efficiency and competitive advantage in the market. Here are some strategies to enhance IP core performance:.

- Utilizing Advanced Algorithms: Implementing advanced algorithms can significantly improve the efficiency of IP cores. Algorithms such as parallel processing, pipelining, and data compression can enhance performance.

- Optimizing Resource Utilization: Efficient resource management is essential for optimizing IP core performance. Utilize resources effectively by minimizing wastage and maximizing utilization.

- Clock Domain Crossing Optimization: Addressing clock domain crossing issues is vital for improving IP core performance. Proper synchronization techniques and design practices can mitigate timing violations.

- Power Optimization Techniques: Implement power optimization techniques to reduce power consumption without compromising performance. Techniques such as clock gating, power gating, and voltage scaling can enhance efficiency.

Strategies for Performance Optimization

To optimize IP core performance, consider the following strategies:.

- Performance Profiling: Conduct performance profiling to identify bottlenecks and areas for improvement. Analyzing performance metrics helps in determining optimization priorities.

- Hardware/Software Co-Design: Implement a hardware/software co-design approach to leverage the strengths of both hardware and software components. This collaborative approach can enhance performance and efficiency.

- FPGA Implementation Best Practices: When targeting FPGA implementation, adhere to best practices such as proper constraint management, timing closure techniques, and efficient resource allocation to optimize performance.

- Continuous Testing and Iteration: Regularly test and iterate on IP core designs to fine-tune performance. Continuous testing helps in identifying issues early and implementing optimizations effectively.

By implementing these strategies and best practices, you can optimize IP core performance and achieve superior efficiency and competitiveness in the digital landscape.

Importance of IP Core Performance Optimization

Optimizing IP core performance is not just about achieving faster processing speeds; it is also about maximizing resource utilization and minimizing power consumption. High-performance IP cores are essential in various applications, including telecommunications, automotive, aerospace, and consumer electronics.

- Telecommunications: In the telecommunications industry, efficient IP core performance is crucial for handling high data volumes, ensuring low latency, and supporting advanced communication protocols. Optimized IP cores enable faster data processing and seamless connectivity.

- Automotive: In the automotive sector, IP core performance optimization is vital for implementing advanced driver assistance systems (ADAS), autonomous driving functionalities, and in-vehicle infotainment systems. Reliable and high-performance IP cores contribute to safe and efficient vehicle operations.

- Aerospace: Aerospace applications rely on high-performance IP cores for real-time data processing, navigation systems, and communication interfaces. Optimized IP cores help in enhancing the performance and reliability of aerospace technologies.

- Consumer Electronics: Consumer electronics devices, such as smartphones, tablets, and smart home appliances, benefit from optimized IP core performance. Efficient processing capabilities enhance user experience, battery life, and overall device functionality.

Future Trends in IP Core Performance Optimization

The field of IP core performance optimization is continuously evolving to meet the increasing demands of modern technologies. Future trends in IP core performance optimization include:.

- AI-Based Optimization: Integration of artificial intelligence (AI) techniques for dynamic performance optimization based on workload demands and system requirements.

- Quantum Computing: Exploration of quantum computing concepts for ultra-fast processing speeds and enhanced computational capabilities in IP core designs.

- Security-Centric Optimization: Focus on security aspects during IP core performance optimization to prevent vulnerabilities and ensure data integrity in connected systems.

- Edge Computing: Utilization of edge computing paradigms to optimize IP core performance for real-time data processing and low-latency applications at the network edge.

By staying updated on these future trends and incorporating innovative approaches, designers and engineers can further enhance IP core performance and drive technological advancements across various industries.

IP Core Security Considerations

Security Measures in IP Core Usage

The use of Intellectual Property (IP) cores has become commonplace in various industries, from consumer electronics to automotive. These pre-designed blocks of code offer a cost-effective and time-saving solution for integrating complex functionalities into electronic systems. However, with the convenience they provide comes the responsibility of ensuring their security. Here are some key security measures to consider when using IP cores:.

- Vendor Trustworthiness: Before integrating an IP core into your design, it’s crucial to assess the trustworthiness of the vendor. Look for reputable suppliers with a track record of delivering secure and reliable IP cores.

- Code Review and Verification: Conduct a thorough review of the IP core’s code to identify any potential security vulnerabilities. Implement code verification processes to ensure that the core performs as intended and is free from malicious code.

- Access Control: Limit access to the IP core within your organization to authorized personnel only. Implement strong access control measures to prevent unauthorized modifications or tampering.

- Regular Updates: Stay informed about security patches and updates provided by the IP core vendor. Regularly update the cores in your designs to address any known vulnerabilities and enhance security.

Protecting IP Cores from Vulnerabilities

While implementing security measures is essential, it’s also important to proactively protect IP cores from potential vulnerabilities. Here are some strategies to safeguard your IP cores:.

- Encryption: Implement encryption mechanisms to protect the confidentiality and integrity of the IP core’s code and data. Encryption helps prevent unauthorized access and tampering.

- Secure Communication: Ensure that communication channels between the IP core and other components in the system are secure. Use protocols like HTTPS and SSH to encrypt data transmission and prevent eavesdropping.

- Hardware Security: Consider implementing hardware security measures, such as secure boot mechanisms and physical tamper resistance, to protect the IP core from attacks targeting the underlying hardware.

By prioritizing security measures and adopting proactive strategies to protect IP cores from vulnerabilities, you can enhance the overall security of your electronic systems and mitigate the risks associated with IP core usage.

Conclusion

Leveraging FPGA IP cores can greatly benefit a design project by providing pre-designed functional blocks that can be easily integrated and customized to meet specific requirements. By carefully selecting the right IP cores, understanding their integration process, and effectively customizing them as needed, developers can significantly reduce time-to-market and development costs while still achieving high performance and reliability in their FPGA-based systems. Embracing FPGA IP cores as a valuable resource can empower engineers to focus more on the unique aspects of their design, leading to innovative solutions and competitive advantages in today’s rapidly evolving technological landscape.