Field-Programmable Gate Arrays (FPGAs) have become a cornerstone in modern digital design, offering unparalleled flexibility and performance for a wide range of applications.

From signal processing and machine learning to networking and embedded systems, FPGAs are increasingly being used to accelerate complex computations. However, as the complexity of these applications grows, so does the demand for memory. While FPGAs come with on-chip memory resources such as Block RAMs (BRAMs) and UltraRAMs, these are often insufficient for large-scale applications. This is where external memory comes into play.

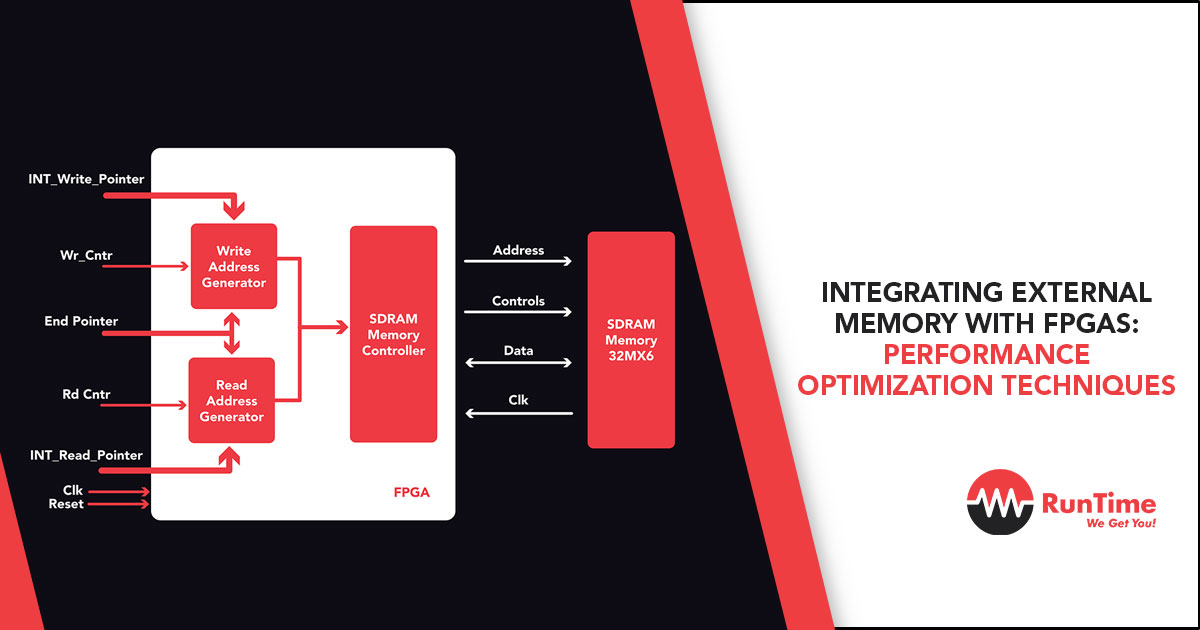

Integrating external memory with FPGAs can significantly enhance the system’s capabilities, but it also introduces a new set of challenges. The performance of an FPGA-based system is heavily dependent on how efficiently it can access and manage external memory. In this article, we will explore various techniques to optimize the performance of FPGA systems when integrating external memory, focusing on memory interfaces, data transfer strategies, and system-level optimizations.

Understanding the Basics: FPGA and External Memory

FPGA Memory Hierarchy

Before diving into external memory integration, it’s essential to understand the memory hierarchy in FPGAs. FPGAs typically have three levels of memory:

- On-Chip Memory (BRAMs/UltraRAMs): These are fast, low-latency memory resources embedded within the FPGA fabric. They are ideal for storing small to medium-sized data sets and are often used for caching or buffering.

- On-Board Memory (DDR SDRAM): Many FPGA development boards come with on-board DDR SDRAM, which offers higher capacity than on-chip memory but with increased latency.

- External Memory (DDR, HBM, Flash): For applications requiring even larger memory capacities, external memory devices such as DDR4, High Bandwidth Memory (HBM), or Flash memory can be used. These memories offer significantly higher storage capacities but come with higher latency and more complex interfacing requirements.

Types of External Memory

When integrating external memory with FPGAs, the choice of memory type is crucial. The most common types of external memory used with FPGAs include:

- DDR SDRAM: Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) is the most commonly used external memory due to its balance of capacity, speed, and cost. DDR4 is the latest generation, offering higher bandwidth and lower power consumption compared to its predecessors.

- High Bandwidth Memory (HBM): HBM is a newer type of memory that offers extremely high bandwidth by stacking multiple memory dies vertically and connecting them to the FPGA via a wide interface. HBM is ideal for applications requiring massive data throughput, such as machine learning and high-performance computing.

- Flash Memory: Flash memory is non-volatile and is often used for storing firmware, configuration data, or large datasets that need to be retained across power cycles. While Flash memory has higher read/write latency compared to DDR SDRAM, it offers much higher storage capacity.

Challenges in Integrating External Memory with FPGAs

Integrating external memory with FPGAs is not without its challenges. Some of the key issues include:

- Latency: External memory access typically involves higher latency compared to on-chip memory. This latency can become a bottleneck, especially in real-time applications.

- Bandwidth: While external memory offers higher capacity, achieving high bandwidth requires careful design of the memory interface and data transfer mechanisms.

- Power Consumption: External memory interfaces can consume significant power, which is a critical consideration in power-constrained embedded systems.

- Complexity: Designing and optimizing the memory interface can be complex, requiring a deep understanding of both the FPGA architecture and the memory device’s characteristics.

Performance Optimization Techniques

To address these challenges, several performance optimization techniques can be employed when integrating external memory with FPGAs. These techniques can be broadly categorized into memory interface optimization, data transfer optimization, and system-level optimization.

1. Memory Interface Optimization

The memory interface is the bridge between the FPGA and the external memory. Optimizing this interface is crucial for achieving high performance.

a. Use High-Speed Memory Controllers

Modern FPGAs come with built-in memory controllers that support high-speed interfaces such as DDR4, LPDDR4, and HBM. These controllers are highly optimized for performance and can significantly reduce the complexity of designing a custom memory interface. When selecting an FPGA, it’s essential to choose one with a memory controller that matches the requirements of your application.

b. Optimize Memory Timing Parameters

Memory timing parameters, such as CAS latency, RAS-to-CAS delay, and precharge time, play a critical role in determining the performance of the memory interface. These parameters can be adjusted to optimize the trade-off between latency and bandwidth. However, care must be taken to ensure that the memory device is operated within its specified limits.

c. Implement Burst Transfers

Burst transfers allow multiple data words to be transferred in a single transaction, reducing the overhead associated with individual memory accesses. Most modern memory controllers support burst transfers, and enabling this feature can significantly improve memory bandwidth.

d. Use Multi-Port Memory Controllers

In applications where multiple FPGA modules need to access the same external memory, a multi-port memory controller can be used to allow concurrent access. This can help reduce contention and improve overall system performance.

2. Data Transfer Optimization

Efficient data transfer between the FPGA and external memory is essential for maximizing performance. The following techniques can help optimize data transfers:

a. Data Alignment and Padding

Ensuring that data is properly aligned and padded can improve memory access efficiency. Misaligned data can result in multiple memory accesses for a single data transfer, increasing latency and reducing bandwidth. By aligning data to the memory’s natural boundaries, you can minimize the number of memory accesses required.

b. Use Direct Memory Access (DMA)

Direct Memory Access (DMA) allows data to be transferred between the FPGA and external memory without involving the CPU. This can significantly reduce the overhead associated with data transfers and free up the CPU for other tasks. Most modern FPGAs come with built-in DMA controllers that can be configured to handle complex data transfer scenarios.

c. Implement Data Prefetching

Data prefetching involves fetching data from external memory before it is actually needed by the FPGA. This can help hide the latency associated with memory access and improve overall system performance. Prefetching can be implemented using hardware or software techniques, depending on the application’s requirements.

d. Optimize Data Granularity

The granularity of data transfers can have a significant impact on performance. Transferring large chunks of data in a single transaction can reduce the overhead associated with memory access and improve bandwidth. However, care must be taken to ensure that the data granularity matches the application’s requirements.

3. System-Level Optimization

In addition to optimizing the memory interface and data transfers, system-level optimizations can further enhance the performance of FPGA systems with external memory.

a. Use Memory Hierarchies

A well-designed memory hierarchy can help balance the trade-off between latency, bandwidth, and capacity. By using on-chip memory for frequently accessed data and external memory for less frequently accessed data, you can reduce the overall latency and improve system performance.

b. Implement Caching Mechanisms

Caching is a powerful technique for reducing memory access latency. By storing frequently accessed data in on-chip memory, you can reduce the number of accesses to external memory and improve overall system performance. Caching can be implemented using hardware or software techniques, depending on the application’s requirements.

c. Optimize Memory Access Patterns

The way data is accessed in memory can have a significant impact on performance. Sequential access patterns are generally more efficient than random access patterns, as they allow for better utilization of burst transfers and prefetching. By optimizing the memory access patterns in your application, you can improve memory bandwidth and reduce latency.

d. Use Parallelism

FPGAs are inherently parallel devices, and leveraging this parallelism can help improve memory performance. By implementing parallel memory access mechanisms, you can increase the overall memory bandwidth and reduce latency. This can be achieved using techniques such as memory interleaving, where multiple memory banks are accessed simultaneously.

e. Power Optimization

Power consumption is a critical consideration in many embedded systems. Optimizing the memory interface and data transfer mechanisms can help reduce power consumption. For example, using low-power memory devices, optimizing memory timing parameters, and reducing the number of memory accesses can all contribute to lower power consumption.

Case Study: Optimizing External Memory Access in a Video Processing Application

To illustrate the practical application of these optimization techniques, let’s consider a case study of a video processing application implemented on an FPGA.

Application Overview

The application involves real-time video processing, where the FPGA is responsible for applying various image processing algorithms to a high-resolution video stream. The video frames are stored in external DDR4 memory, and the FPGA needs to access these frames efficiently to perform the required processing.

Challenges

The primary challenges in this application are:

- High Bandwidth Requirement: The video stream requires high bandwidth to transfer large frames between the FPGA and external memory.

- Low Latency: Real-time processing requires low-latency memory access to ensure that the video frames are processed and displayed without delay.

- Power Consumption: The system is power-constrained, so power-efficient memory access is essential.

Optimization Techniques

To address these challenges, the following optimization techniques were employed:

- High-Speed DDR4 Memory Controller: The FPGA’s built-in DDR4 memory controller was used to achieve high-speed memory access. The controller was configured to optimize timing parameters and enable burst transfers.

- DMA for Data Transfers: DMA was used to transfer video frames between the FPGA and external memory. This reduced the overhead associated with CPU involvement and improved data transfer efficiency.

- Data Prefetching: Data prefetching was implemented to hide the latency of memory access. The FPGA prefetched video frames from external memory before they were needed for processing.

- Memory Hierarchy: A memory hierarchy was implemented, with on-chip BRAMs used for storing frequently accessed data (e.g., lookup tables for image processing algorithms) and external DDR4 memory used for storing video frames.

- Parallel Memory Access: Memory interleaving was used to access multiple DDR4 memory banks in parallel, increasing the overall memory bandwidth.

- Power Optimization: Low-power DDR4 memory devices were used, and the memory interface was optimized to reduce power consumption.

Results

By applying these optimization techniques, the video processing application achieved the following results:

- High Bandwidth: The system achieved the required bandwidth to handle the high-resolution video stream, with burst transfers and parallel memory access contributing to the high data throughput.

- Low Latency: Data prefetching and optimized memory access patterns reduced the latency of memory access, ensuring real-time video processing.

- Power Efficiency: The power-optimized memory interface and low-power memory devices helped meet the system’s power constraints.

Conclusion

Integrating external memory with FPGAs is a powerful way to enhance the capabilities of FPGA-based systems, but it requires careful optimization to achieve high performance. By optimizing the memory interface, data transfer mechanisms, and system-level design, you can overcome the challenges associated with external memory integration and unlock the full potential of your FPGA-based system.

Whether you’re working on a video processing application, a machine learning accelerator, or a high-performance computing system, the techniques discussed in this article can help you achieve the performance, latency, and power efficiency required for your application.

As FPGAs continue to evolve, with new memory technologies and interfaces emerging, the importance of optimizing external memory integration will only grow. By staying informed and applying these optimization techniques, you can ensure that your FPGA-based systems remain at the cutting edge of performance and efficiency.