Introduction

High-Level Synthesis (HLS) has emerged as a game-changer in FPGA development, offering a significant leap in productivity and design efficiency. By enabling the use of C/C++ for hardware design, HLS bridges the gap between software and hardware development, empowering engineers to focus on algorithm development rather than low-level hardware implementation details. This article delves into the intricacies of HLS, explores its benefits, and provides practical guidance on leveraging HLS tools for accelerated FPGA development.

Understanding High-Level Synthesis

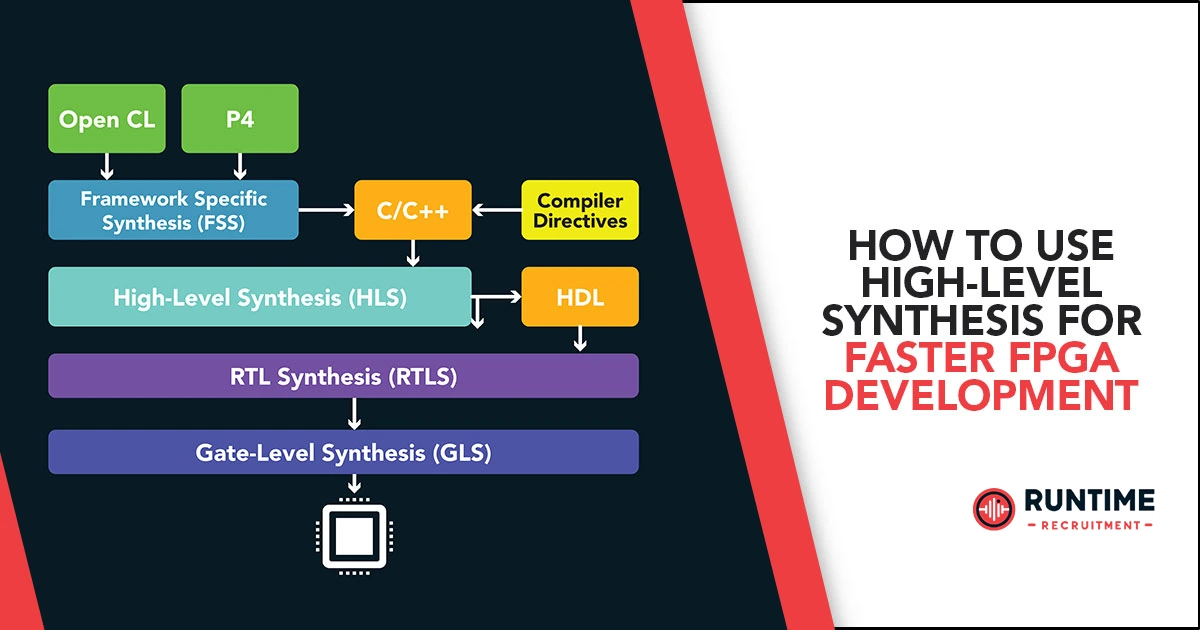

HLS is a design methodology that automates the process of converting high-level code, typically written in C or C++, into hardware-specific Register Transfer Level (RTL) code. This RTL code can then be synthesized into a physical FPGA configuration. By abstracting away the complexity of hardware design, HLS empowers engineers to explore design alternatives rapidly and iterate on their designs efficiently.

Key Benefits of HLS:

- Increased Design Productivity: HLS significantly reduces development time by allowing engineers to work at a higher level of abstraction.

- Improved Design Verification: HLS tools often provide advanced simulation and debugging capabilities, facilitating early design validation.

- Accelerated Time-to-Market: By shortening the design cycle, HLS enables faster product development and deployment.

- Reusability of Software Code: Existing software algorithms can be repurposed for hardware acceleration, leveraging existing intellectual property.

- Exploration of Design Alternatives: HLS tools enable rapid prototyping and experimentation with different hardware architectures.

HLS Tools and Workflow

Several commercial and open-source HLS tools are available, each with its strengths and weaknesses. Popular options include:

- Xilinx Vivado HLS: A comprehensive HLS tool integrated into the Xilinx Vivado Design Suite.

- Intel FPGA HLS Compiler: Provides HLS capabilities for Intel FPGAs, with a focus on performance optimization.

- Synopsys Vitis HLS: Offers advanced HLS features and supports a wide range of FPGA targets.

The typical HLS workflow involves the following steps:

- Algorithm Development: Write the algorithm in C/C++ using HLS-specific constructs and directives.

- Synthesis: The HLS tool translates the C/C++ code into RTL code, optimizing for performance and resource utilization.

- RTL Simulation: Verify the generated RTL code using simulation to ensure functional correctness.

- FPGA Implementation: Synthesize the RTL code into an FPGA configuration, including place and route.

- Hardware Verification: Test the FPGA implementation to validate performance and meet design requirements.

Best Practices for HLS

To maximize the benefits of HLS and achieve optimal results, consider the following best practices:

- Algorithm Optimization: Profile the algorithm to identify performance bottlenecks and optimize accordingly.

- Dataflow and Control Flow Partitioning: Carefully structure the code to balance dataflow and control flow for efficient hardware implementation.

- Memory Hierarchy Optimization: Optimize memory access patterns and consider using on-chip memory resources effectively.

- Pipeline Optimization: Identify pipelining opportunities to improve performance and resource utilization.

- Constraint Specification: Provide clear and accurate constraints to guide the HLS tool in generating optimal hardware.

- Iterative Design Process: Use HLS to explore different design alternatives and refine the implementation based on results.

Advanced HLS Techniques

To unlock the full potential of HLS, explore advanced techniques such as:

- Custom Data Types: Define custom data types to match hardware-specific data representations.

- Array Partitioning: Optimize memory access by partitioning arrays into smaller chunks.

- Interface Synthesis: Generate efficient interfaces for communication with other hardware components.

- Timing Constraints: Specify timing requirements to guide the HLS tool in meeting performance targets.

- Power Optimization: Explore techniques to reduce power consumption in the generated hardware.

In-Depth Guide to HLS Workflow

Algorithm Development

The first step in HLS is to develop the algorithm in a high-level language, typically C or C++. This involves writing the code with consideration for hardware implementation, including the use of HLS-specific constructs and directives. These constructs help the HLS tool understand how to map the high-level code onto hardware resources.

For example, consider an image processing algorithm that performs edge detection. The algorithm can be written in C/C++ with loop unrolling and pipelining directives to optimize hardware implementation. The use of these directives helps the HLS tool generate efficient RTL code that can be synthesized into a high-performance FPGA configuration.

Synthesis

Once the algorithm is developed, the next step is synthesis. The HLS tool takes the high-level code and translates it into RTL code. This process involves optimizing the code for performance and resource utilization. The tool analyzes the code, identifies parallelism opportunities, and generates a hardware description that meets the specified constraints.

During synthesis, the HLS tool may also provide feedback on the generated RTL code, including performance metrics and resource usage. This feedback can be used to refine the algorithm and improve the overall design.

RTL Simulation

After synthesis, the generated RTL code must be verified through simulation. RTL simulation ensures that the synthesized hardware behaves correctly and meets the functional requirements. Simulation tools can be used to test the RTL code against various input scenarios and validate its functionality.

In the case of the image processing algorithm, RTL simulation would involve providing different images as input and verifying that the output matches the expected results. This step is crucial for identifying any functional issues and ensuring the correctness of the generated hardware.

FPGA Implementation

Once the RTL code is verified, the next step is FPGA implementation. This involves synthesizing the RTL code into a physical FPGA configuration, including place and route. The FPGA toolchain maps the RTL code onto the FPGA’s hardware resources, optimizing for performance and area.

The implementation process also includes generating the bitstream that can be programmed onto the FPGA. This bitstream represents the final hardware configuration and is used to configure the FPGA for the desired functionality.

Hardware Verification

The final step in the HLS workflow is hardware verification. This involves testing the FPGA implementation to validate its performance and ensure it meets the design requirements. Hardware verification can be done using test benches and real-world scenarios to ensure the FPGA performs as expected.

In the case of the image processing algorithm, hardware verification would involve running the algorithm on the FPGA with various images and measuring its performance. This step helps identify any performance bottlenecks and ensures the FPGA implementation meets the desired specifications.

Advanced HLS Techniques Explained

Custom Data Types

Custom data types are essential in HLS for matching hardware-specific data representations. Engineers can optimize data storage and processing for the target hardware by defining custom data types. This involves specifying bit widths and data formats that align with the hardware architecture, ensuring efficient resource utilization.

Array Partitioning

Array partitioning is a technique used to optimize memory access by dividing large arrays into smaller, more manageable chunks. This approach reduces memory access latency and improves parallelism, leading to better performance. In HLS, array partitioning can be achieved using directives that guide the tool in splitting arrays appropriately.

Interface Synthesis

Interface synthesis is the process of generating efficient communication interfaces for hardware components. HLS tools can automatically generate interfaces such as AXI or FIFO for communication between different hardware modules. Proper interface synthesis ensures seamless data transfer and synchronization between hardware components.

Timing Constraints

Timing constraints are critical in guiding the HLS tool to meet performance targets. By specifying timing requirements, engineers can ensure the generated hardware meets the desired clock frequency and latency. Timing constraints help the HLS tool optimize the design for speed, balancing performance, and resource utilization.

Power Optimization

Power optimization techniques are essential for reducing power consumption in FPGA designs. HLS tools offer various power optimization strategies, such as clock gating and power-aware synthesis. By leveraging these techniques, engineers can design energy-efficient hardware that meets power budget requirements.

Challenges and Solutions in HLS

While HLS offers numerous benefits, it also presents certain challenges that engineers must address to achieve optimal results. Some common challenges and their solutions include:

Performance Bottlenecks

One of the primary challenges in HLS is identifying and mitigating performance bottlenecks. Performance issues can arise from inefficient memory access, insufficient parallelism, or suboptimal pipelining. To address these bottlenecks, engineers can:

- Profile the Algorithm: Use profiling tools to identify performance-critical sections of the code.

- Optimize Memory Access: Implement techniques such as array partitioning and loop unrolling to improve memory access patterns.

- Increase Parallelism: Leverage pipelining and parallel processing to maximize the utilization of hardware resources.

Resource Utilization

Efficient resource utilization is crucial for achieving high-performance FPGA designs. Overuse of hardware resources can lead to increased power consumption and reduced performance. To optimize resource utilization, engineers can:

- Refine Data Representations: Use custom data types to match the hardware’s capabilities.

- Balance Dataflow and Control Flow: Structure the code to balance data processing and control logic, ensuring efficient hardware implementation.

- Specify Accurate Constraints: Provide clear constraints to guide the HLS tool in generating resource-efficient hardware.

Debugging and Verification

Debugging and verification are essential steps in the HLS workflow. Ensuring the correctness of the generated hardware requires thorough testing and validation. To enhance debugging and verification, engineers can:

- Leverage Advanced Simulation Tools: Use simulation tools with advanced debugging capabilities to identify and fix functional issues.

- Implement Test Benches: Develop comprehensive test benches to validate the functionality of the RTL code.

- Perform Hardware-in-the-Loop Testing: Test the FPGA implementation in real-world scenarios to ensure it meets the design requirements.

Conclusion

High-Level Synthesis is a powerful tool that can significantly accelerate FPGA development while improving design quality. By understanding the fundamentals of HLS and following best practices, engineers can harness its potential to create innovative and high-performance FPGA-based systems. As HLS technology continues to evolve, we can expect even greater productivity gains and expanded application areas in the future.

In summary, HLS offers a transformative approach to FPGA development by enabling the use of high-level languages like C/C++ for hardware design. This methodology bridges the gap between software and hardware development, empowering engineers to focus on algorithm development and innovation. By leveraging advanced HLS techniques and addressing common challenges, engineers can unlock the full potential of HLS, leading to faster, more efficient, and higher-quality FPGA designs.

Hire the Best Engineers with RunTime

At RunTime, we are dedicated to helping you find the best Engineering talent for your recruitment needs. Our team consists of engineers-turned-recruiters with an extensive network and a focus on quality. By partnering with us, you will have access to great engineering talent that drives innovation and excellence in your projects.

Discover how RunTime has helped 423+ tech companies find highly qualified and talented engineers to enhance their team’s capabilities and achieve strategic goals.

On the other hand, if you’re a control systems engineer looking for new opportunities, RunTime Recruitment’s job site is the perfect place to find job vacancies.