In the realm of high-performance computing, the fusion of OpenCL and FPGAs presents a compelling opportunity for developers to unlock unprecedented power and efficiency. This guide delves into the intricate world of harnessing the capabilities of OpenCL on FPGAs, offering a roadmap for developers to navigate this cutting-edge technology landscape.

Open Computing Language (OpenCL) provides a versatile framework for programming heterogeneous systems, while Field-Programmable Gate Arrays (FPGAs) offer customizable hardware acceleration. By marrying these two technologies, developers can achieve optimal performance and scalability in their computing applications.

Throughout this guide, we will explore the fundamentals of OpenCL, delve into the unique advantages of FPGAs, and provide practical insights for developers looking to leverage this potent combination. Join us on this journey as we uncover the vast potential of OpenCL on FPGAs and empower developers to push the boundaries of computational innovation.

Understanding OpenCL and FPGAs

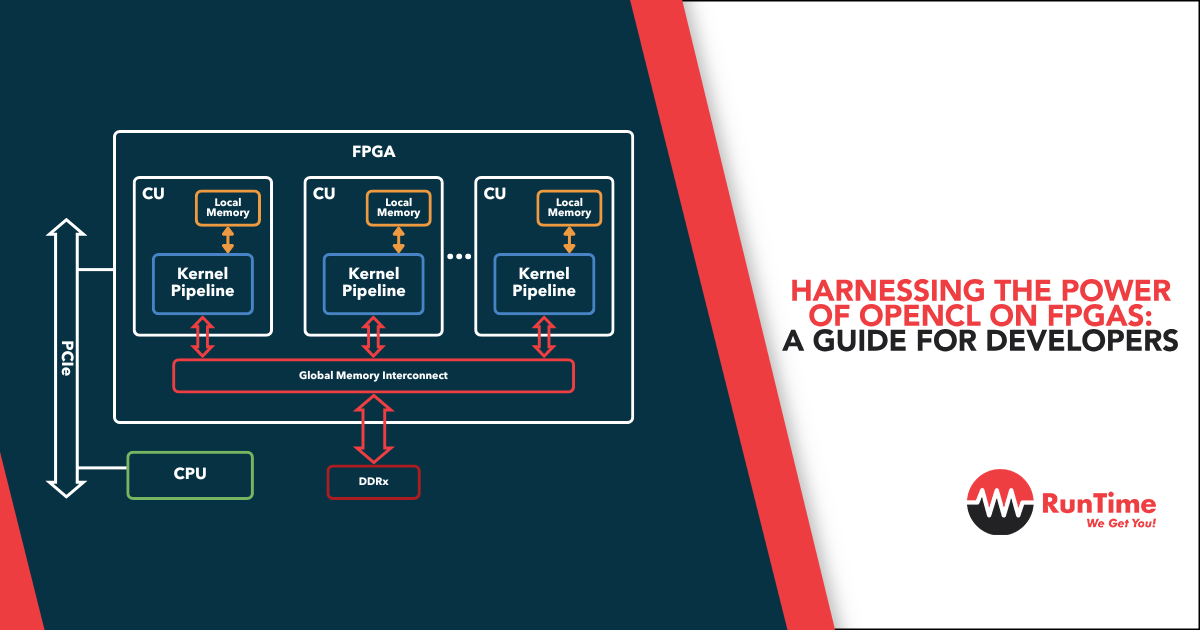

OpenCL, short for Open Computing Language, is a framework for writing programs that execute across heterogeneous platforms, including CPUs, GPUs, FPGAs, and other processors. It allows developers to write code in a single language that can be executed across different hardware accelerators.

FPGAs, or Field-Programmable Gate Arrays, are integrated circuits designed to be configured by a customer or a designer after manufacturing. They are highly flexible and can be reprogrammed to perform specific tasks efficiently.

When used together, OpenCL and FPGAs provide a powerful combination for accelerating computations in various applications. OpenCL allows developers to write code in a high-level language and target FPGAs for hardware acceleration.

Benefits of using OpenCL on FPGAs:

- Performance: OpenCL on FPGAs can significantly accelerate computational tasks compared to running them on traditional CPUs or GPUs.

- Flexibility: FPGAs can be reprogrammed for different tasks, allowing for flexibility in implementing and optimizing algorithms.

- Energy Efficiency: FPGAs are known for their energy efficiency, making them a suitable choice for applications where power consumption is a concern.

- Low Latency: FPGAs can offer low latency for processing tasks, which is crucial in real-time applications such as signal processing or video processing.

- Parallel Processing: FPGAs excel at parallel processing, enabling high throughput for tasks that can be parallelized effectively.

- Custom Hardware Acceleration: With OpenCL on FPGAs, developers can create custom hardware accelerators tailored to their specific applications, optimizing performance.

- Real-Time Processing: The combination of OpenCL and FPGAs is ideal for real-time processing requirements, providing low latency and high performance for time-sensitive applications.

- Scalability: FPGAs offer scalability options, allowing for the development of scalable solutions that can adapt to changing computational requirements.

The collaboration of OpenCL and FPGAs opens up a new realm of possibilities in the field of hardware acceleration. By leveraging OpenCL’s portability and FPGAs’ adaptability, developers can harness the full potential of these technologies to address complex computational challenges across various industries.

One of the key advantages of utilizing OpenCL on FPGAs is the ability to create domain-specific accelerators that are tailored to specific applications. This level of customization allows for optimized performance and efficiency, especially in scenarios where off-the-shelf solutions may fall short.

Moreover, the synergy between OpenCL and FPGAs is not limited to performance gains alone. By integrating these technologies, developers can explore novel approaches to algorithm optimization and parallel processing, pushing the boundaries of what is achievable in terms of computational speed and efficiency.

In addition to performance enhancements, the use of FPGAs with OpenCL can lead to significant cost savings in the long run. The reconfigurability of FPGAs means that hardware resources can be utilized more efficiently, reducing the need for frequent hardware upgrades and minimizing operational expenses.

Furthermore, the combination of OpenCL and FPGAs fosters innovation in real-time processing applications, enabling the development of cutting-edge solutions for industries such as autonomous vehicles, medical imaging, and financial modeling. The low latency and high throughput capabilities of FPGAs make them an attractive choice for time-sensitive tasks that demand swift and accurate data processing.

By embracing the convergence of OpenCL and FPGAs, developers can unlock a myriad of opportunities to revolutionize computational workflows, drive technological advancements, and accelerate progress in diverse fields. The dynamic interplay between these technologies not only elevates performance standards but also sets the stage for pioneering developments that have the potential to shape the future of computing.

Setting up Development Environment

Requirements for OpenCL Development on FPGAs

To start developing with OpenCL on FPGAs, you need to ensure your system meets certain requirements. This includes having a compatible FPGA board, the necessary software tools, and a basic understanding of OpenCL programming.

Tools Needed for Development Setup

- FPGA Board: Select an FPGA board that supports OpenCL development. Some popular options include Intel FPGA boards and Xilinx FPGA boards.

- OpenCL SDK: Download and install the appropriate OpenCL SDK for your FPGA board. This SDK will provide the necessary libraries and tools for OpenCL development.

- Development Environment: Choose an integrated development environment (IDE) for coding in OpenCL. Quartus Prime for Intel FPGAs and Vivado for Xilinx FPGAs are commonly used.

Installation Procedures

- Install the FPGA Board Drivers: Before connecting your FPGA board to the development system, make sure to install the required drivers. These drivers enable communication between the FPGA board and your computer.

- Setup OpenCL SDK: Follow the installation instructions provided by the FPGA board manufacturer to set up the OpenCL SDK on your system. This typically involves running an installer and configuring the SDK settings.

- Configure the Development Environment: Once the SDK is installed, configure your chosen IDE to work with the OpenCL SDK. This may involve setting paths to the SDK libraries and tools.

Additional Considerations

- Understanding OpenCL Programming: Familiarize yourself with the principles of OpenCL programming, such as parallel computing and memory management, to leverage the full potential of FPGA acceleration.

- FPGA Board Selection: Research and compare different FPGA boards based on your project requirements, performance benchmarks, and compatibility with OpenCL.

- Version Compatibility: Ensure that the versions of the OpenCL SDK, development tools, and drivers are compatible to avoid any compatibility issues during development.

Conclusion

Setting up a development environment for OpenCL programming on FPGAs requires careful consideration of hardware, software tools, and programming knowledge. By following the outlined steps and considering additional factors, you can create an efficient and optimized environment for FPGA development using OpenCL.

By incorporating these additional considerations, you can enhance your development experience and optimize your FPGA-based projects for performance and efficiency.

Writing and Optimizing OpenCL Kernels

In the realm of FPGA development, mastering the craft of writing and optimizing OpenCL kernels holds the key to unlocking unparalleled performance on FPGA devices. Here’s a comprehensive exploration of the essential strategies and best practices for achieving optimal results.

Crafting Efficient OpenCL Kernels for FPGAs

Efficiency in OpenCL kernel authoring for FPGAs demands a deep understanding of the FPGA’s architecture. To harness the full potential of the device, developers must tailor their kernel code to capitalize on its strengths. This involves fine-tuning memory access patterns, reducing data transfers between the host and the device, and implementing effective parallelization techniques to fully exploit the parallel processing capabilities of the FPGA.

Performance Optimization Strategies

Optimizing code for peak performance requires a systematic approach of profiling, analysis, and refinement. Techniques like loop unrolling, pipelining, and leveraging FPGA-specific resources such as block RAMs and DSP slices can significantly boost the execution speed of OpenCL kernels. It’s imperative to work within the constraints of the FPGA, considering factors like resource availability and memory bandwidth, to achieve optimal performance levels.

Embracing Best Practices in Kernel Development

Following established best practices in kernel development can streamline the optimization journey and pave the way for maintainable code. By structuring kernels in a modular and scalable manner, incorporating vectorization when appropriate, and embracing software-hardware co-design principles, developers can maximize the performance potential of their FPGA-based solutions.

Leveraging High-Level Synthesis for Productivity

High-level synthesis (HLS) tools offer a productive alternative for FPGA kernel development by allowing developers to write in higher-level languages like C, C++, or OpenCL, which are automatically transformed into hardware descriptions. This abstraction simplifies the development process, enabling faster iteration cycles and facilitating code reuse across projects. By harnessing the power of HLS, developers can expedite the implementation of complex algorithms on FPGAs while maintaining a focus on algorithmic efficiency and performance optimization.

Harnessing Vendor-Specific Optimization Techniques

Different FPGA vendors provide proprietary optimization techniques and tools to enhance the performance of OpenCL kernels on their devices. Leveraging vendor-specific libraries, directives, and optimizations tailored to the FPGA architecture can yield significant performance gains. It’s essential for developers to explore and exploit these vendor-specific features to fine-tune their kernel implementations and achieve the best possible performance outcomes.

Mastering the art of writing and optimizing OpenCL kernels for FPGAs is a multifaceted endeavor that demands a blend of architectural understanding, performance optimization strategies, adherence to best practices, and utilization of advanced development tools. By honing these skills and embracing the evolving landscape of FPGA technology, developers can unlock the full potential of FPGA-based acceleration and drive innovation across various domains, from high-performance computing to real-time signal processing and beyond.

Maximizing Resource Utilization

Maximizing resource utilization is crucial for achieving optimal performance and efficiency. Here are some strategies to efficiently use FPGA resources:

Strategies to Efficiently Use FPGA Resources:

Implementing design optimization techniques such as pipelining, loop unrolling, and resource sharing can help in maximizing the utilization of FPGA resources. By carefully analyzing the design requirements and implementing these strategies, developers can make the most out of the available resources.

- Memory Management Techniques:

Efficient memory management is essential for maximizing resource utilization in FPGA designs. Utilizing memory efficiently, implementing memory hierarchy, and optimizing memory access patterns can significantly impact the overall performance of the design. Techniques like memory banking, data prefetching, and memory compression can further enhance memory utilization and performance.

- Utilizing Parallelism:

Leveraging parallelism is key to maximizing resource utilization in FPGA designs. By parallelizing operations, developers can distribute the workload across multiple resources, thereby improving performance and throughput. Techniques such as task parallelism, data parallelism, and pipeline parallelism can be employed to effectively utilize the available resources and accelerate computations.

- Hardware/Software Co-Design:.

Adopting a hardware/software co-design approach can optimize resource utilization by offloading certain tasks to software components, thereby freeing up FPGA resources for critical operations. This approach enhances flexibility, scalability, and performance by efficiently partitioning tasks between hardware and software.

- Dynamic Power Management:.

Implementing dynamic power management techniques such as voltage and frequency scaling, clock gating, and power gating can optimize resource utilization by dynamically adjusting power consumption based on the workload requirements. By intelligently managing power, developers can maximize performance while minimizing energy consumption.

- Resource Sharing and Virtualization:

Exploring resource sharing techniques like time-division multiplexing and virtualization can further enhance resource utilization in FPGA designs. By efficiently allocating resources based on task requirements and dynamically adjusting resource allocation, developers can optimize resource utilization and improve design flexibility.

- Advanced Compilation and Synthesis Techniques:

Employing advanced compilation and synthesis techniques can help in optimizing resource utilization by generating efficient hardware configurations. Techniques such as high-level synthesis, constraint-based synthesis, and optimization for specific FPGA architectures can streamline the design process and maximize resource utilization.

- Performance Profiling and Optimization:.

Conducting performance profiling and optimization iterations can fine-tune resource utilization in FPGA designs. By analyzing performance bottlenecks, optimizing critical paths, and balancing resource usage, developers can ensure efficient resource allocation and enhanced design performance.

By incorporating these advanced strategies and techniques into FPGA design practices, developers can enhance resource utilization, optimize performance, and achieve efficient designs that meet the demands of today’s complex applications.

Performance Optimization Techniques

Optimizing the performance of software applications is crucial to ensure that they meet user expectations and deliver a seamless experience. Let’s delve deeper into some key techniques that developers can employ to enhance the performance of their applications.

1. Profiling and Benchmarking for Performance Tuning

Profiling and benchmarking are essential tools for developers looking to fine-tune their applications for optimal performance. Profiling involves analyzing the performance of a program by measuring various metrics such as execution time, memory usage, and CPU utilization. By identifying bottlenecks and areas of inefficiency, developers can make targeted improvements to boost performance. Benchmarking, on the other hand, allows developers to compare the performance of different implementations, enabling them to choose the most efficient approach for their specific use case.

2. Vectorization and Pipelining Methods

Vectorization and pipelining are advanced optimization techniques that can significantly enhance the performance of software applications, especially in scenarios where high computational efficiency is critical. Vectorization involves executing operations on multiple data elements simultaneously, leveraging parallel processing capabilities to expedite computations. On the other hand, pipelining breaks down the execution of instructions into smaller stages, enabling overlapping operations and reducing latency, thus improving overall throughput.

- Algorithm Optimization

Algorithm optimization plays a pivotal role in boosting the efficiency of software applications by focusing on enhancing the underlying algorithms. Developers can achieve algorithm optimization by refining algorithms to reduce time complexity and space complexity. This optimization can be realized through strategic selection of data structures, elimination of redundant computations, and implementation of more efficient algorithms tailored to specific requirements.

- Caching Strategies for Performance Enhancement

Caching is a powerful technique used to store frequently accessed data in a temporary storage location, reducing the need to recalculate or retrieve the same data repeatedly. By implementing caching mechanisms such as in-memory caches or distributed caches, developers can significantly improve application performance by reducing response times and minimizing resource utilization.

- Parallelism and Concurrency Techniques

Utilizing parallelism and concurrency techniques allows applications to execute multiple tasks simultaneously, leveraging the capabilities of multi-core processors and distributed computing environments. By dividing tasks into smaller subtasks that can be processed concurrently, developers can enhance application responsiveness, scalability, and throughput, leading to improved overall performance.

By integrating these diverse performance optimization techniques into their development practices, developers can create software applications that not only meet but exceed performance expectations. The result is high-performing software that delivers superior responsiveness, scalability, and user satisfaction. Stay tuned for more comprehensive insights on maximizing software performance in our upcoming articles!.

Testing and Debugging Strategies

Comprehensive Testing Methodologies for OpenCL on FPGAs

Ensuring the reliability and performance of OpenCL designs on FPGAs requires a systematic approach to testing. This section will delve into comprehensive testing methodologies, focusing on unit testing, integration testing, and performance testing.

- Unit Testing: Unveiling the Foundation

Unit testing involves assessing individual components or modules of the OpenCL design in isolation to ensure their correctness and functionality. By isolating specific units, developers can detect and rectify errors early in the development cycle, promoting code quality and reliability.

- Integration Testing: Harmonizing the Ensemble

Integration testing evaluates how different modules interact within the system, detecting interface issues or compatibility conflicts that may arise when components are combined. By validating the integration of various modules, developers can verify system behavior and functionality, ensuring seamless operation.

- Performance Testing: Optimizing Resource Utilization

Performance testing evaluates the overall performance of the OpenCL design across various workloads and conditions. By analyzing resource utilization and throughput metrics, developers can identify bottlenecks and optimize the design for enhanced efficiency and speed.

Advanced Debugging Tools and Techniques

Debugging complex FPGA designs demands a diverse toolkit of tools and techniques. Beyond the basics, this section will explore advanced debugging tools such as Xilinx Vivado Logic Analyzer and Intel Quartus SignalTap.

- Advanced Debugging Techniques: Harnessing Real-Time Insights

Advanced debugging tools empower developers to delve deep into the FPGA’s internal operation, facilitating the identification and resolution of complex issues. By utilizing tools like logic analyzers and signal probes, developers can streamline the debugging process, accelerating time-to-resolution and improving overall design efficiency.

Proactive Error Handling Strategies and Troubleshooting Techniques

Effective error handling is paramount in FPGA development to maintain system stability and reliability. This section will introduce proactive error handling strategies, including built-in self-testing mechanisms, redundant resources, and fault-tolerant design practices.

- Troubleshooting Techniques: Navigating Challenges with Precision

In the event of errors, troubleshooting becomes a critical aspect of FPGA development. Common troubleshooting techniques such as signal probing, waveform analysis, and RTL simulation enable developers to diagnose issues accurately and expedite the resolution process. By honing troubleshooting skills, developers can effectively address challenges, ensuring optimal system performance and reliability.

Real-world Implementations

1. Case Studies of Successful OpenCL Projects on FPGAs

In this section, we will delve into compelling case studies that highlight the success stories of OpenCL projects implemented on FPGAs. These case studies will showcase how the synergy between OpenCL and FPGA technology has revolutionized industries such as healthcare, finance, and automotive. By exploring the intricacies of these projects, we will uncover the innovative solutions that have propelled them to success, setting new benchmarks for high-performance computing.

- Challenges Faced and Solutions Implemented

As we navigate through the landscape of OpenCL projects on FPGAs, we will confront the various challenges that developers and engineers encountered along the way. From tackling issues related to power consumption and latency to optimizing resource utilization, each challenge presented an opportunity for creative problem-solving. By elucidating the strategies and methodologies employed to overcome these hurdles, we aim to provide valuable insights for aspiring FPGA programmers and researchers seeking to push the boundaries of computational efficiency.

- Future Prospects and Trends

Peering into the horizon of technological innovation, we will speculate on the future prospects and emerging trends in the domain of OpenCL and FPGA integration. The evolving synergy between these technologies is poised to redefine the landscape of high-performance computing, opening doors to unprecedented opportunities in areas such as artificial intelligence, data analytics, and scientific research. Join us as we anticipate the transformative impact of OpenCL-FPGA integration and explore the uncharted realms of possibility that lie ahead.

Embark on a captivating journey through the real-world implementations of OpenCL projects on FPGAs in this comprehensive blog section. Gain profound insights, glean inspiration from industry visionaries, and immerse yourself in the limitless potential of FPGA-accelerated computing. Stay tuned for a captivating exploration of innovation, challenges, and the boundless horizons of technological advancement in the realm of FPGA programming.

Conclusion

Embracing the potential of OpenCL on FPGAs can significantly enhance the performance and efficiency of developers’ projects. By leveraging the parallel processing capabilities of FPGAs through OpenCL, developers can optimize their applications for a wide range of tasks. This guide has shed light on the benefits and techniques for harnessing this power, paving the way for developers to explore new possibilities in their projects and stay at the forefront of innovation.