The world of embedded systems is in constant flux, driven by relentless innovation. At its heart, Field-Programmable Gate Arrays (FPGAs) continue to be a cornerstone for rapid prototyping, specialized acceleration, and flexible hardware solutions. Yet, for all their power, FPGAs present a formidable challenge that has plagued engineers for decades: documentation. Specifically, the leap from highly technical Register-Transfer Level (RTL) code to clear, comprehensive, and human-readable specifications.

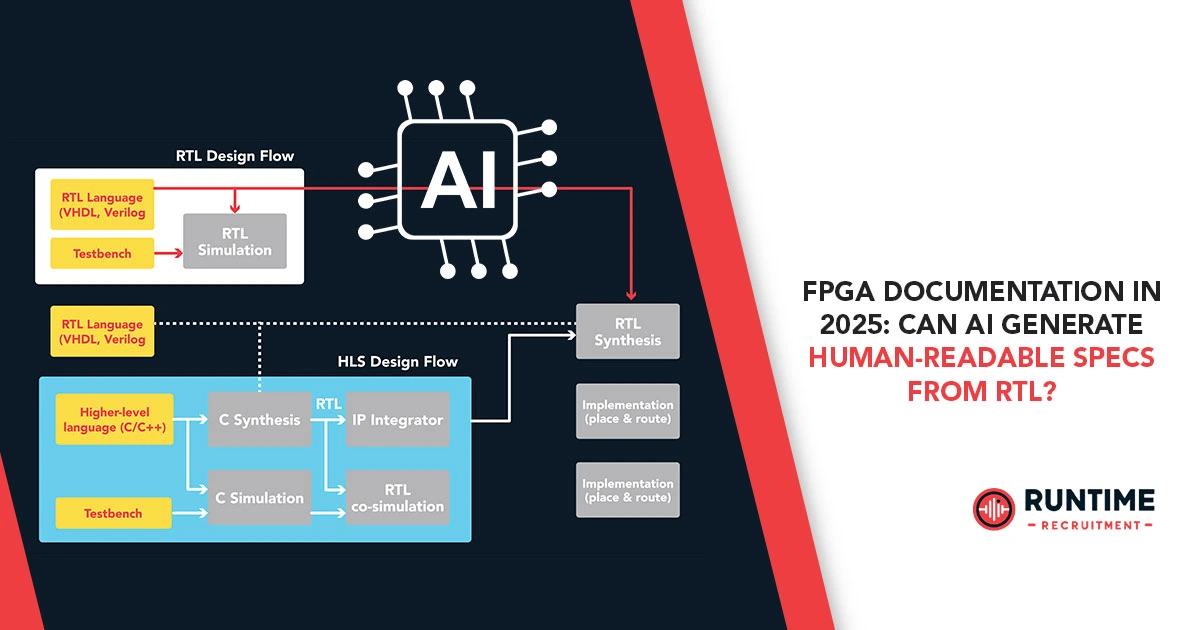

In 2025, with the meteoric rise of Artificial Intelligence (AI), particularly large language models (LLMs), the question isn’t just a hopeful whisper but a serious inquiry: Can AI bridge this chasm? Can it truly transform intricate RTL into documentation that even a non-FPGA expert can understand, fostering collaboration and accelerating development? This article dives deep into the possibilities, the current state, the inherent challenges, and the exciting future of AI-driven FPGA documentation.

The Perennial Pain Point: FPGA Documentation

Ask any experienced embedded engineer about their biggest headaches, and “documentation” will inevitably be high on the list. For FPGAs, this pain is amplified. RTL, written in Verilog, VHDL, or SystemVerilog, describes the hardware’s behavior at a granular level – how data moves between registers, the control logic, and timing. It’s precise, unambiguous, and essential for synthesis and implementation. However, it’s also dense, verbose, and optimized for machine interpretation, not human comprehension.

Consider a complex FPGA design with thousands of lines of RTL across multiple modules. To understand the system’s high-level functionality, its interfaces, its performance characteristics, and its error handling mechanisms, one typically needs detailed design specifications, user guides, and verification plans. Manually creating and maintaining these documents is a monumental task. It’s time-consuming, prone to errors, often lags behind design changes, and requires significant effort from senior engineers who could be focusing on core design work.

This documentation gap leads to:

- Reduced Productivity: Engineers spend less time designing and more time documenting or trying to decipher undocumented code.

- Knowledge Silos: Critical design knowledge remains locked in the heads of a few experts, making onboarding new team members difficult and increasing project risk if key personnel leave.

- Increased Debugging Time: Without clear specifications, tracing unexpected behavior or understanding system interactions becomes a convoluted, trial-and-error process.

- Compliance Challenges: For industries with strict regulatory requirements (e.g., aerospace, medical), thorough and up-to-date documentation is non-negotiable.

- Integration Headaches: When integrating FPGA IP into larger systems, poorly documented modules become bottlenecks, demanding extensive communication and reverse engineering.

The desire for automated, intelligent documentation solutions is not new, but the capabilities of AI in 2025 have fundamentally shifted the landscape.

The Promise of AI: From RTL to Readable Specs

The core premise is compelling: leverage AI, specifically large language models (LLMs) and potentially specialized AI architectures, to analyze RTL code and generate natural language descriptions of its functionality. This isn’t just about syntax highlighting or basic code comments; it’s about extracting the intent behind the design.

Here’s how AI could theoretically achieve this:

- Semantic Understanding of RTL: Traditional parsers understand the syntax of HDL. AI, particularly advanced LLMs trained on vast datasets of code and natural language, can go deeper. They can learn to identify common design patterns (e.g., state machines, FIFOs, arithmetic units, bus interfaces) and infer their purpose. They can recognize architectural choices and how different modules interact.

- Contextual Awareness: A key challenge in translating code to human-readable text is maintaining context. A single line of RTL might seem trivial, but its meaning is deeply intertwined with surrounding logic, port definitions, and even external specifications. AI models can be trained to retain this context, understanding data flow, control signals, and timing relationships.

- Natural Language Generation (NLG): Once the AI has a robust understanding of the RTL’s function, it can employ NLG techniques to articulate this understanding in clear, concise, and human-readable prose. This could range from high-level architectural overviews to detailed descriptions of individual module behavior, interface protocols, and timing constraints.

- Hierarchical Documentation: Complex FPGA designs are structured hierarchically. AI could generate documentation that mirrors this hierarchy, providing summaries at the top level and allowing users to drill down into specific modules for more granular details.

- Automated Comment Generation and Refactoring: Beyond full specifications, AI could automatically generate meaningful comments for RTL code, improving its intrinsic readability. It could also suggest refactoring opportunities to make the RTL more understandable and therefore easier to document.

- Error and Anomaly Detection: As a side benefit, an AI system trained to understand “correct” RTL patterns and their corresponding documentation could potentially flag anomalies or potential bugs in the RTL itself if it struggles to generate a coherent description.

The Current State of Play in 2025

While the vision is ambitious, significant progress has been made. We are no longer talking about purely theoretical concepts.

- Code Generation and Refactoring: AI-powered tools are already assisting engineers in generating simple RTL logic, refactoring existing code for better readability, and even porting designs between different HDL languages. Tools like GitHub Copilot, when properly prompted, can suggest HDL snippets and generate basic test benches. This demonstrates AI’s ability to understand and manipulate RTL.

- High-Level Synthesis (HLS) Integration: HLS tools, which allow engineers to describe hardware at a higher abstraction level (e.g., C/C++), are increasingly integrating AI to optimize the translation to efficient RTL. While not direct documentation, this shows AI’s role in bridging abstraction gaps in hardware design.

- Formal Verification Assistance: AI is being used to assist in formal verification, learning from past bugs and predicting likely failure points, which indirectly contributes to a deeper understanding of the design’s behavior, a prerequisite for robust documentation.

- Early-Stage Documentation Pilots: Some companies and research institutions are actively experimenting with using LLMs to generate initial drafts of design specifications from RTL. These efforts often involve providing the LLM with the RTL code, potentially some existing high-level architectural notes, and specific prompts to guide the output. The results are not always perfect, requiring human oversight and refinement, but they offer a significant head start compared to manual efforts.

- Focus on Readability Enhancements: Specific research projects are exploring how language models can take generated RTL (which is often hard to read) and rewrite it into a more human-friendly format, complete with meaningful comments, while ensuring logic equivalence. This is a direct attack on the documentation problem.

However, it’s crucial to acknowledge the limitations in 2025:

- “Hallucinations” and Accuracy: LLMs, by their nature, can “hallucinate” or generate plausible-sounding but incorrect information. In hardware, where precision is paramount, a single misinterpretation could lead to catastrophic design flaws. This necessitates rigorous human review and verification of any AI-generated documentation.

- Complexity and Scale: While AI can handle simpler modules, scaling this to multi-million gate designs with intricate interactions and obscure corner cases remains a significant challenge. The sheer volume of RTL and the depth of its dependencies can overwhelm current models.

- Understanding Intent vs. Behavior: AI excels at describing what the RTL does (its behavior). It’s far harder for it to infer why a particular design choice was made (the designer’s intent). This deeper level of understanding is often crucial for comprehensive documentation.

- Proprietary IP and Data Privacy: Training robust AI models requires vast amounts of data. Using proprietary RTL code for training without proper safeguards raises significant intellectual property and data privacy concerns for many companies.

- Lack of Domain-Specific Training Data: While general-purpose LLMs are powerful, they are not inherently optimized for the nuances of hardware description languages. Creating truly effective AI for FPGA documentation might require extensive training on curated, high-quality RTL and corresponding human-written specifications, which is a resource-intensive endeavor.

The Path Forward: Hybrid Approaches and Specialized AI

The most likely scenario for FPGA documentation in the near future is not full automation, but rather a powerful human-AI collaboration.

- AI as a “Documentation Co-Pilot”: Engineers will leverage AI tools to generate first drafts, summarize complex blocks, suggest comments, and cross-reference information. The human engineer then acts as an editor, refining, validating, and adding the critical context and intent that AI currently struggles with.

- Specialized AI Models: Instead of general-purpose LLMs, we may see the emergence of AI models specifically fine-tuned on vast datasets of RTL, hardware specifications, and design patterns. These domain-specific models would be far more accurate and nuanced in their understanding of hardware.

- Integration with EDA Tools: Expect deeper integration of AI capabilities directly into Electronic Design Automation (EDA) tools. Imagine a “document” button in your Vivado or Quartus environment that generates an initial spec for a selected module.

- Structured Inputs and Prompt Engineering: Engineers will become adept at “prompt engineering” – crafting precise inputs and queries to AI models to guide the documentation generation process. This could involve providing high-level natural language descriptions of desired functionality alongside the RTL.

- Verification of Documentation: Just as RTL undergoes rigorous verification, the AI-generated documentation will also need its own verification process, potentially using formal methods or cross-referencing against simulation results.

- Living Documentation: AI could facilitate “living documentation” – where changes in the RTL automatically trigger updates or flags for review in the associated documentation, ensuring consistency and preventing documentation drift.

The benefits of such a hybrid approach are immense. It promises to drastically reduce the time and effort spent on documentation, improve its quality and consistency, and free up valuable engineering time for innovation. For embedded engineers, this means less tedious writing and more focus on the exciting challenges of design and optimization.

Beyond RTL: A Holistic Documentation Future

While the focus here is on RTL to human-readable specs, AI’s impact on FPGA documentation extends further:

- Testbench and Verification IP Documentation: AI can analyze verification environments and test scenarios to generate documentation for testbenches, verification IP, and coverage reports.

- Performance and Resource Reports: From synthesis and implementation reports, AI could generate clear summaries of performance metrics (Fmax, latency), resource utilization (LUTs, FFs, DSPs, BRAMs), and power consumption estimates.

- Migration and Porting Guides: AI could analyze differences between different FPGA architectures or design versions and automatically generate guides for migrating or porting designs.

- Troubleshooting and Debugging Guides: By analyzing past bug reports, simulation logs, and design knowledge bases, AI could assist in generating troubleshooting guides and common debugging tips for specific IP blocks or system configurations.

The ultimate goal is a more intelligent, integrated, and less burdensome documentation workflow, allowing embedded engineers to spend their time creating, not transcribing.

Conclusion: A New Era of Efficiency and Collaboration

The year 2025 stands at the cusp of a significant transformation in how FPGA documentation is created and consumed. While the idea of AI autonomously generating flawless, human-readable specifications from raw RTL might still be a few years off for highly complex, novel designs, the strides made in AI, particularly with large language models, point towards an undeniable future of AI-assisted documentation.

This isn’t about replacing the embedded engineer; it’s about empowering them. By offloading the tedious, error-prone tasks of manual documentation, AI allows engineers to focus on higher-value activities: architectural innovation, design optimization, and tackling the truly hard problems. The era of the “documentation co-pilot” is upon us, promising to accelerate development cycles, enhance knowledge transfer, and ultimately, bring more sophisticated and reliable FPGA-based systems to market faster.

The embedded engineering landscape is evolving, and with it, the tools and methodologies we employ. Embracing AI for documentation is not just an efficiency gain; it’s a strategic imperative for staying competitive and fostering a more productive and collaborative design environment.

Are you an embedded engineer looking to work at the forefront of this technological revolution?

RunTime Recruitment specializes in connecting top-tier embedded engineers with cutting-edge opportunities in companies that are pushing the boundaries of what’s possible.

Whether you’re deeply involved in AI-driven hardware design, exploring innovative documentation methodologies, or simply seeking your next challenging role, we can help you find the perfect fit.

Connect with RunTime Recruitment today to discuss your next career move.