FPGA (Field Programmable Gate Array) design quality is paramount in the ever-evolving world of technology. A high-quality FPGA design can significantly impact product performance, reliability, and time-to-market. Moreover, it ensures efficient utilization of resources, thus reducing overall development costs.

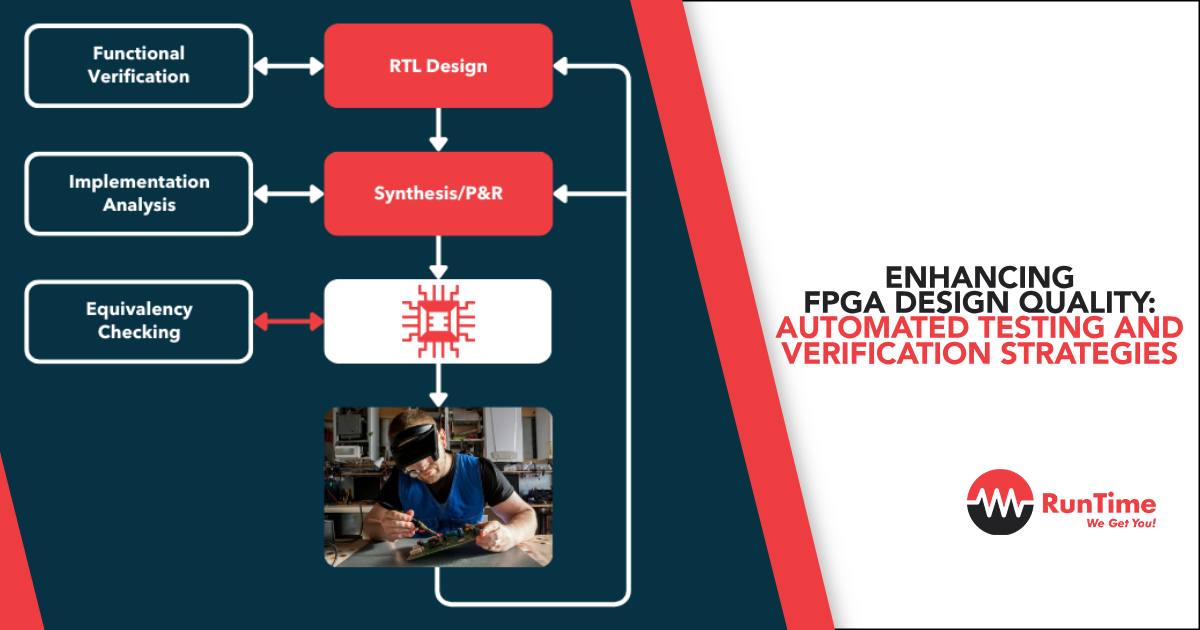

Designing high-quality FPGAs is a complex process that involves multiple stages, from coding and synthesis to implementation and verification. Ensuring design quality can be challenging due to tight deadlines, a rapidly changing technology landscape, and the need to balance design performance with power and cost constraints. Additionally, manual verification and testing methods can be time-consuming and error-prone.

Automated testing and verification strategies have emerged as a vital solution to the challenges associated with FPGA design quality. These strategies can help designers identify and fix design errors early in the development process, reduce verification efforts, and improve overall design quality. Furthermore, automated testing and verification provide a more efficient and accurate approach compared to traditional manual methods, allowing designers to meet stringent performance and reliability requirements.

Overview of the FPGA Design Process

FPGA Basics and Architecture

FPGAs are integrated circuits that can be reprogrammed to perform a wide range of digital functions. They consist of programmable logic blocks and interconnects, allowing designers to create custom circuits by configuring these elements. FPGA architectures typically include lookup tables (LUTs), flip-flops, and other components such as embedded memory blocks and digital signal processing (DSP) blocks.

Design Entry: Coding and Synthesis

The first step in the FPGA design process is design entry, where engineers create the desired digital circuit using a hardware description language (HDL) like VHDL or Verilog. The HDL code describes the functionality and structure of the design. Following design entry, synthesis tools convert the HDL code into a gate-level netlist, which represents the design using logic gates and interconnects.

Implementation: Place and Route

After synthesis, the design moves to the implementation stage. During implementation, place, and route (P&R) tools map the gate-level netlist to the FPGA’s programmable logic resources. The P&R process involves assigning specific FPGA resources to the design elements and routing the interconnects to establish the required connections. It aims to optimize the design for performance, power consumption, and resource utilization.

Verification and Testing

Verification and testing are crucial steps in the FPGA design process, ensuring the correctness and quality of the design. Verification involves checking the design against its specifications, while testing ensures the design functions correctly when implemented on the FPGA. Various verification and testing techniques, such as simulation, formal methods, and prototyping, are employed to validate the design and identify errors.

Deployment and Debugging

Once the design is verified and tested, it is deployed to the FPGA. The deployment process involves generating a bitstream file, which configures the FPGA’s programmable elements to implement the design. After deployment, designers may perform debugging and performance analysis, using tools such as logic analyzers and on-chip debugging features to identify and resolve any remaining issues.

Related Article: FPGA Design Flow

Automated Testing Strategies for FPGA Designs

Types of Automated Testing

Unit Testing

Unit testing focuses on testing individual design components, such as modules or blocks, in isolation. Automated unit testing tools generate testbenches and simulate the behavior of the design components for various input scenarios. This approach helps identify issues at the component level, making it easier to pinpoint and fix errors.

Integration Testing

Integration testing verifies the interaction between multiple design components. It ensures that the combined functionality of interconnected components works correctly and meets the design specifications. Automated integration testing tools can generate testbenches and simulate the behavior of the integrated design, helping designers identify and fix any issues arising from component interactions.

System Testing

System testing evaluates the entire FPGA design as a whole, simulating its operation in the target system environment. It verifies that the design meets the overall system requirements and functions correctly under various conditions. Automated system testing tools can simulate different system scenarios and analyze the design’s performance, ensuring that it meets the desired specifications.

Benefits of Automated Testing

Faster Testing Cycles

Automated testing significantly reduces the time required to test FPGA designs. By automating the generation of testbenches and simulations, designers can quickly identify and fix issues, accelerating the overall design process. This enables faster time-to-market and improved productivity.

Improved Accuracy and Reliability

Automated testing reduces the risk of human error, ensuring higher accuracy and reliability in the testing process. By using automated tools, designers can generate exhaustive test scenarios and execute tests consistently, improving the overall quality of the FPGA design.

Enhanced Design Quality

Automated testing helps designers identify issues early in the design process, enabling them to fix errors before they become more difficult to address. This leads to higher design quality, improved performance, and increased confidence in the final product.

Automated Verification Strategies for FPGA Designs

Formal Verification Methods

Model Checking

Model checking is a formal verification technique that systematically examines the behavior of a design against a set of properties or specifications. It uses mathematical algorithms to prove the correctness of the design, ensuring that it meets the desired requirements. Automated model checking tools can help designers identify and fix errors early in the development process, improving the overall quality and reliability of the FPGA design.

Equivalence Checking

Equivalence checking is another formal verification method that compares two representations of a design, such as the HDL code and the synthesized netlist, to ensure they are functionally equivalent. Automated equivalence checking tools can quickly identify discrepancies between the design representations, helping designers detect and correct synthesis errors or optimizations that may have altered the intended functionality.

Simulation-Based Verification Methods

Static Timing Analysis

Static timing analysis (STA) is a simulation-based verification technique that analyzes the timing behavior of a design without requiring actual simulation. STA tools compute the timing paths and delays in the design, ensuring that it meets the specified timing constraints. Automated STA tools can quickly identify critical paths and timing violations, enabling designers to optimize the design for performance and power consumption.

Dynamic Simulation

Dynamic simulation involves executing the design in a simulated environment, observing its behavior for various input scenarios and conditions. Automated simulation tools can generate testbenches, apply stimuli, and analyze the design’s response to verify its correctness and performance. By automating the simulation process, designers can quickly identify and fix issues, reducing the overall verification effort and improving design quality.

Benefits of Automated Verification

Detecting Design Errors Early

Automated verification methods help designers detect design errors early in the development process, enabling them to fix issues before they become more challenging to address. This leads to higher design quality, improved performance, and increased confidence in the final product.

Reducing Verification Time

Automated verification tools significantly reduce the time required for verification, accelerating the overall design process. By automating tasks such as testbench generation and simulation, designers can focus on addressing identified issues, ultimately achieving faster time-to-market and improved productivity.

Ensuring Design Correctness and Performance

Automated verification techniques ensure the correctness and performance of the FPGA design by rigorously checking it against its specifications. This leads to higher design quality, improved reliability, and increased confidence in the final product’s functionality and performance.

Best Practices for Implementing Automated Testing and Verification Strategies

Adopting a Verification-Driven Design Approach

A verification-driven design approach involves incorporating verification activities throughout the design process, ensuring that the design meets its specifications at every stage. By adopting this approach, designers can identify and fix issues early, reducing the risk of errors and improving the overall design quality.

Developing Reusable Testbenches and Components

Creating reusable testbenches and components can significantly streamline the verification process. By developing modular and parameterized testbenches, designers can easily adapt them for different design components and scenarios, reducing the time and effort required for verification.

Using Industry-Standard Verification Languages and Tools

Employing industry-standard verification languages, such as SystemVerilog or VHDL, and tools ensures compatibility and interoperability with other designs and tools. By using standardized languages and tools, designers can leverage existing libraries and resources, further accelerating the verification process and ensuring consistent results.

Leveraging Continuous Integration and Version Control Systems

Continuous integration and version control systems can help manage the design and verification process more efficiently. By automating the build, test, and deployment process, continuous integration ensures that the design is consistently verified against the latest changes. Version control systems track and manage changes in the design, allowing designers to revert to previous versions if issues arise, and collaborate more effectively.

Collaborating with Cross-Functional Teams for Efficient Verification

Collaborating with cross-functional teams, such as software developers, hardware engineers, and verification engineers, can greatly enhance the verification process. By sharing knowledge, resources, and expertise, designers can more effectively identify and address issues, ensuring a higher-quality FPGA design.

Case Studies: Success Stories of Enhanced FPGA Design Quality Using Automated Testing and Verification

Example 1: Improved Time-to-Market and Design Reliability

A leading telecommunications company faced challenges in meeting stringent time-to-market requirements while ensuring design reliability for their FPGA-based product. By implementing automated testing and verification strategies, the company was able to detect design errors early in the development process and fix them promptly. The automated approach enabled the company to reduce the overall verification effort, resulting in faster time-to-market and a more reliable product. Ultimately, this led to increased customer satisfaction and a competitive edge in the market.

Example 2: Reduced Verification Effort and Increased Design Confidence

An automotive technology firm was developing an FPGA-based system for advanced driver assistance systems (ADAS). The design complexity and performance requirements demanded rigorous verification to ensure the system’s safety and reliability. By adopting automated testing and verification strategies, the company was able to streamline the verification process and reduce the effort required to validate the design. This approach not only saved time and resources but also increased the design team’s confidence in the final product, ensuring its successful deployment in the target application.

Conclusion

In the rapidly evolving world of technology, FPGA design quality is critical to product performance and success. Automated testing and verification strategies play a significant role in enhancing design quality, ensuring that FPGA designs meet the stringent requirements of performance, reliability, and time-to-market.

By adopting automated testing and verification strategies, designers can detect and fix errors early in the development process, reduce verification effort, and improve overall design quality. This leads to better product performance, increased customer satisfaction, and a competitive edge in the market.

The role of industry professionals and engineering recruitment is crucial in fostering FPGA design quality. RunTime Recruitment’s expertise in matching candidates with the right positions and providing prompt and efficient service to clients contributes to the development of high-quality FPGA designs that drive innovation and success in the industry. Discover how RunTime Recruitment can help you find the right talent to enhance your FPGA design quality and accelerate your product’s success.

Hire Highly Skilled Engineers with RunTime Recruitment

Our expert team of engineers-turned-recruiters offers in-depth knowledge of technical recruiting in the engineering industry.

If your company is looking to recruit highly-skilled engineers worldwide, contact us today and we will do the sourcing for you. Or if you’re an engineer looking for new opportunities, you can check RunTime Recruitment’s job site for job vacancies.