Traditional software-based cryptography can become a bottleneck, especially with the growing volume of data and ever-increasing encryption complexities. This is where Field Programmable Gate Arrays (FPGAs) enter the scene, offering a compelling solution for hardware-accelerated cryptography.

This article delves into the practicalities of implementing hardware acceleration for cryptographic algorithms using FPGA resources. We’ll explore the key considerations, design choices, and potential benefits to achieve significantly faster encryption and decryption.

Identifying Bottlenecks: Where Software Falls Short

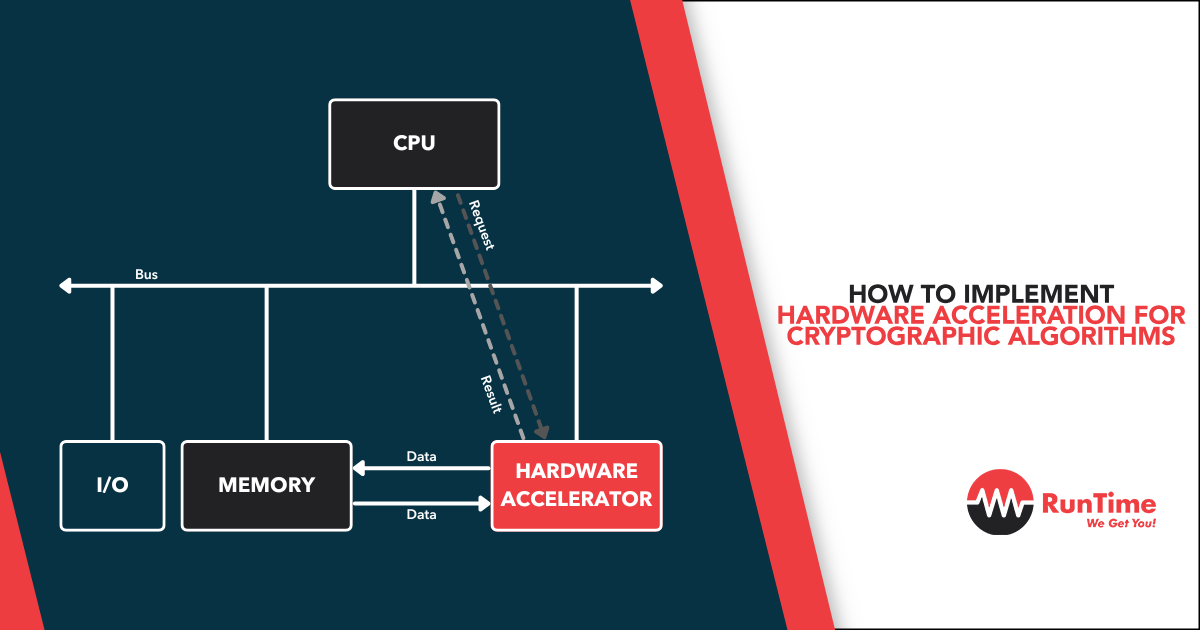

Software-based cryptography, while widely used, suffers from inherent limitations. General-purpose CPUs are not optimized for the intensive mathematical operations that form the core of many encryption algorithms. This leads to:

- Limited Instruction Set: CPUs lack specialized instructions for cryptographic functions, forcing reliance on software emulation, which is computationally expensive.

- Memory Access Bottlenecks: Frequent data movement between CPU and memory during encryption/decryption operations adds significant overhead.

These limitations translate to real-world performance issues:

- Latency Issues: Delays in encryption/decryption can hinder real-time applications like secure communication or high-speed data transfers.

- Reduced Throughput: Slower processing limits the amount of data that can be encrypted/decrypted per unit time.

Unleashing the Power of FPGAs: A Hardware Advantage

FPGAs offer a compelling alternative. These versatile devices are essentially blank canvases of logic gates that can be configured to implement custom hardware tailored for specific tasks. This allows for:

- Parallelization: Multiple cryptographic operations can be executed concurrently on the FPGA, significantly improving performance compared to the sequential nature of software execution.

- Custom Instructions: Dedicated hardware blocks can be designed to perform specific cryptographic functions efficiently, bypassing the limitations of CPU instruction sets.

- Reduced Memory Overhead: Data can be processed directly on the FPGA fabric, minimizing the need for frequent memory accesses.

The result? Hardware acceleration using FPGAs can achieve significant performance gains, leading to:

- Lower Latency: Encryption/decryption operations happen much faster, enabling real-time processing for latency-sensitive applications.

- Higher Throughput: FPGAs can handle larger data volumes with ease, making them ideal for high-performance security systems.

Delving into Design Considerations: Making the Most of FPGAs

Now that we’ve established the advantages of FPGAs, let’s explore some key design considerations for implementing hardware-accelerated cryptography:

- Algorithm Selection: Not all algorithms are equally suited for FPGA implementation. Factors like resource utilization, parallelism potential, and security strength need careful evaluation. Popular choices include AES, RSA, and SHA-3.

- Resource Allocation: FPGAs have a finite number of logic cells and memory blocks. Striking a balance between performance and resource utilization is crucial for optimal design.

- Design Security: Security remains paramount. Implementing countermeasures against side-channel attacks and ensuring proper key management are essential considerations.

- Integration with Existing Systems: The FPGA design needs to seamlessly integrate with the existing software environment for smooth operation.

Advanced Techniques for Innovation:

For experienced engineers seeking a deeper dive, here are some innovative approaches:

- Pipelining: Breaking down the cryptographic algorithm into stages processed concurrently on the FPGA can further enhance performance.

- Loop Unrolling: Unrolling loops in the hardware design reduces control overhead and improves efficiency.

- Custom Datapaths: Designing custom datapaths tailored to specific algorithms can unlock significant performance benefits.

A Pragmatic Approach: Balancing Performance and Cost

While FPGAs offer impressive performance gains, it’s important to maintain a pragmatic perspective.

- Development Time: Designing and implementing FPGA-based cryptography requires specialized expertise and can be more time-consuming than software solutions.

- Non-recurring Engineering (NRE) Costs: The initial investment in FPGA development tools and hardware can be higher compared to software solutions.

- Power Consumption: FPGAs generally consume more power than software implementations. This may be a concern for battery-powered devices.

However, the performance benefits often outweigh these drawbacks, especially for applications where speed and security are critical.

Wrapping Up: Empowering the Future of Cryptography with FPGAs

Hardware acceleration using FPGAs offers a powerful approach to address the performance limitations of software-based cryptography. By carefully considering design choices, innovative techniques, and pragmatic considerations, field engineers can unlock significant performance gains, enabling faster and more secure data encryption for a wide range of applications. As the demand for robust security solutions continues to grow, FPGAs are poised to play a vital role in shaping the future of cryptography.

Hire the Best Engineers with RunTime

At RunTime, we are dedicated to helping you find the best Engineering talent for your recruitment needs. Our team consists of engineers-turned-recruiters with an extensive network and a focus on quality. By partnering with us, you will have access to great engineering talent that drives innovation and excellence in your projects.

Discover how RunTime has helped 423+ tech companies find highly qualified and talented engineers to enhance their team’s capabilities and achieve strategic goals.

On the other hand, if you’re a control systems engineer looking for new opportunities, RunTime Recruitment’s job site is the perfect place to find job vacancies.