Real-Time Anomaly Detection for Predictive Maintenance Using TinyML

Introduction Embedded systems are at the heart of modern industrial automation, IoT devices, and smart infrastructure. One of the most

Introduction Embedded systems are at the heart of modern industrial automation, IoT devices, and smart infrastructure. One of the most

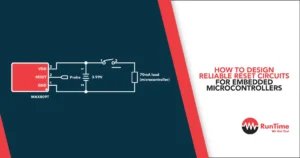

In the world of embedded systems, the reset circuit is a critical component that ensures the microcontroller starts up correctly

In the world of embedded systems, firmware design is becoming increasingly complex. With the proliferation of connected devices, the Internet

High-Performance Computing (HPC) has become a cornerstone of modern technology, enabling breakthroughs in fields such as artificial intelligence, scientific research,

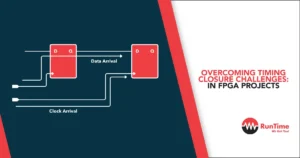

Field-Programmable Gate Arrays (FPGAs) are powerful tools for embedded engineers, offering the flexibility to implement custom hardware designs and accelerate

Embedded systems are increasingly being deployed in harsh environments, from the scorching heat of industrial furnaces to the freezing cold

Ensuring deterministic behavior in real-time embedded systems is paramount for their reliability and performance. The ability to predict precisely how

In the rapidly evolving world of electronics, the demand for smaller, faster, and more efficient devices is driving innovation at

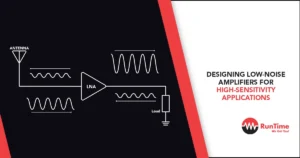

In the realm of embedded systems, particularly those involving high-sensitivity applications such as medical devices, wireless communication, and scientific instrumentation,

Firmware updates are an essential part of maintaining and improving embedded systems, especially in the era of the Internet of