The relentless pursuit of higher performance in FPGA designs has placed an increasing emphasis on clock management. In this digital age, where speed is paramount, mastering clocking techniques is no longer a luxury but a necessity. This article delves into advanced clocking strategies, providing a comprehensive understanding of how to optimize clock signals for peak FPGA performance. We will explore various techniques, their implications, and practical considerations for successful implementation.

As FPGA designs grow more complex and demand higher speeds, the role of clocking becomes even more critical. Effective clock management can be the difference between a design that barely meets specifications and one that exceeds performance expectations. This guide aims to arm you with the knowledge and tools needed to tackle advanced clocking challenges and achieve superior results in your FPGA projects.

Understanding the Clock Domain

Before diving into advanced techniques, it’s crucial to grasp the fundamentals of clock domains. A clock domain is a region of a circuit synchronized to a single clock source. Multiple clock domains coexist in most FPGAs, often leading to challenges in data transfer and synchronization. Understanding clock domain crossing (CDC) and its associated hazards is essential to prevent metastable states and ensure data integrity.

Clock Domain Crossing (CDC)

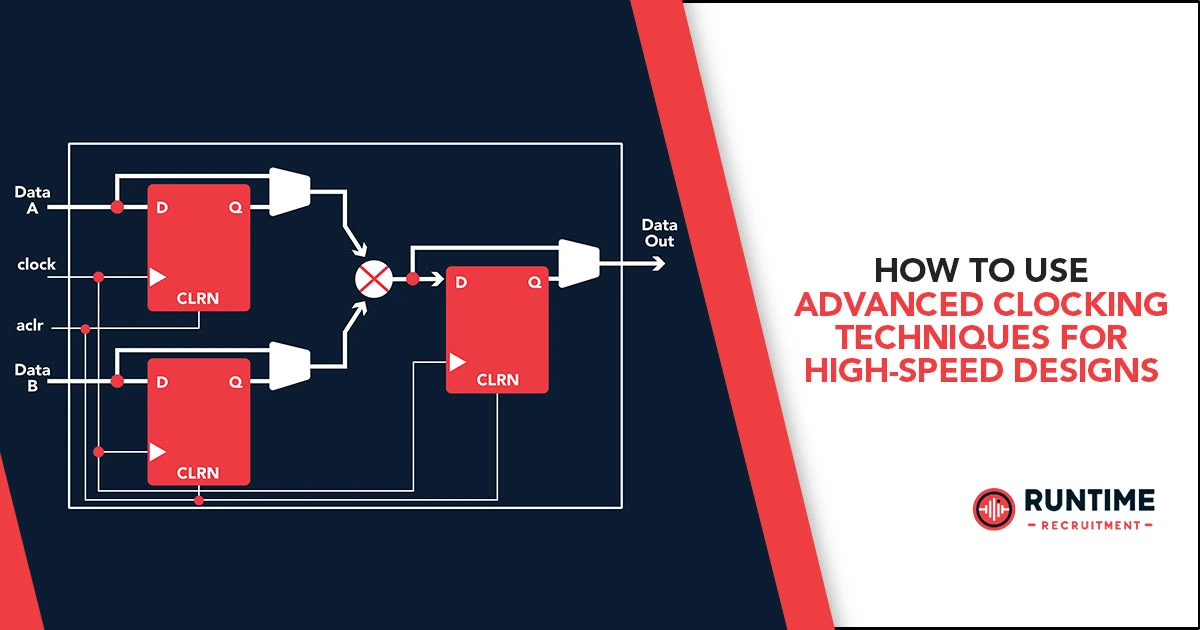

CDC occurs when signals are transferred between different clock domains. This transfer can lead to metastability, a condition where a flip-flop or latch enters an undefined state, potentially causing unpredictable behavior. To mitigate CDC issues, designers must implement synchronization techniques such as:

- Two-Flip-Flop Synchronizer: A simple yet effective method where a signal is passed through two flip-flops in the destination clock domain, reducing the likelihood of metastability.

- Asynchronous FIFOs: These are used for buffering data between different clock domains, allowing safe and reliable data transfer.

- Handshaking Protocols: Implementing handshaking mechanisms ensures that data is safely transferred and acknowledged between clock domains.

The Importance of Clock Domains

Clock domains are integral to the design of FPGAs, especially in systems with varying clock requirements. Different blocks within an FPGA may operate at different frequencies, necessitating careful clock domain management to ensure overall system stability and performance. Properly handling clock domains not only improves performance but also enhances the robustness and reliability of the design.

Advanced Clocking Techniques

To achieve high-speed FPGA designs, advanced clocking techniques must be employed. These techniques focus on optimizing the clock distribution network, generating precise clock signals, reducing power consumption, and ensuring reliable operation across various conditions.

1. Clock Distribution Network (CDN) Optimization

A well-designed CDN is the backbone of any high-speed FPGA. Here are key considerations:

Clock Skew Management

Minimizing clock skew, the difference in arrival times of a clock signal at different points in the circuit, is crucial. Techniques to manage clock skew include:

- Buffer Insertion: Strategically placing buffers along the clock paths to balance delays and ensure synchronous arrival of clock signals.

- Delay Compensation: Using delay elements to equalize path delays, ensuring that all parts of the circuit receive the clock signal simultaneously.

- Careful Routing: Designing clock paths to minimize the differences in routing lengths, thus reducing skew.

Jitter Reduction

Jitter refers to the variations in clock signal timing, which can adversely affect the performance of high-speed circuits. To minimize jitter:

- Low-Jitter Clock Sources: Utilizing high-quality, low-jitter oscillators or crystal clocks as the primary clock source.

- Proper Clock Tree Synthesis: Designing the clock tree to minimize the accumulation of jitter through the network.

Power Integrity

Ensuring adequate power supply to the CDN is vital for maintaining signal integrity. Voltage drops and power supply noise can cause clock signal degradation. Techniques to maintain power integrity include:

- Decoupling Capacitors: Placing capacitors near clock buffers to stabilize the power supply.

- Power Distribution Networks: Designing robust power distribution networks to deliver stable voltage levels to clocking components.

Termination

Using appropriate termination techniques helps match the characteristic impedance of the clock lines, reducing signal reflections and ensuring clean clock signals. Termination methods include:

- Series Termination: Placing a resistor in series with the clock line to match the impedance and absorb reflections.

- Parallel Termination: Using resistors to ground or supply voltage at the end of the clock line to match impedance.

2. Phase-Locked Loops (PLLs) for Clock Generation

PLLs are versatile components for generating multiple clock frequencies and phases from a single reference clock. Effective PLL utilization is crucial:

PLL Placement

Strategically placing PLLs within the FPGA to minimize noise and coupling effects. PLLs should be located away from noisy digital circuits and power supply regions to ensure stable operation.

Loop Filter Design

Optimizing loop filter parameters for PLLs is essential for maintaining stability and achieving a good transient response. The loop filter affects the bandwidth and damping factor of the PLL, influencing its ability to lock onto the reference clock.

Output Buffering

Using appropriate output buffers to drive the clock load ensures that the PLL-generated clock signals maintain their integrity and meet the timing requirements of the connected circuitry.

Jitter Performance

Considering PLL jitter specifications and their impact on the overall system. Low-jitter PLLs contribute to better system performance by providing clean and stable clock signals.

3. Clock Gating

Clock gating can reduce power consumption by dynamically enabling and disabling clock signals. However, it introduces design challenges:

Gating Cell Selection

Choosing appropriate gating cells based on performance and power requirements. Different gating cells offer various trade-offs between power savings and the complexity of implementation.

Metastability Handling

Implementing proper synchronization logic to prevent metastable states when enabling or disabling clocks. This ensures that gated clocks do not introduce timing hazards.

Power Optimization

Balancing power savings with performance impact. Clock gating can significantly reduce power consumption in idle or low-activity modules, but it must be carefully designed to avoid degrading system performance.

4. Clock Tree Synthesis (CTS)

CTS is a critical step in FPGA design, aiming to minimize clock skew and delay. Advanced CTS techniques include:

Buffer Insertion

Strategically inserting buffers along clock paths to balance delays and reduce skew. This ensures that all parts of the circuit receive the clock signal with minimal variation in timing.

Delay Compensation

Using delay elements to compensate for path length differences. This technique helps in aligning clock arrival times across different parts of the FPGA.

Optimization Goals

Defining appropriate CTS optimization goals based on design requirements. These goals might include minimizing clock skew, reducing power consumption, or achieving specific timing margins.

5. Low-Power Clocking Techniques

Power consumption is a major concern in high-speed FPGAs. Consider these low-power clocking strategies:

Dynamic Voltage and Frequency Scaling (DVFS)

Adjusting clock frequency and supply voltage based on workload to save power during periods of low activity. DVFS can dynamically scale down the frequency and voltage, reducing power consumption without compromising performance.

Clock Gating

Effectively implementing clock gating to reduce power in idle or low-activity modules. Clock gating can be applied at various levels of the design hierarchy to maximize power savings.

Multi-Voltage Domains

Creating different voltage domains for different circuit blocks to optimize power consumption. This approach allows high-performance blocks to operate at higher voltages while low-power blocks run at lower voltages.

Practical Considerations and Design Methodology

Implementing advanced clocking techniques requires careful planning and a robust design methodology. Here are key considerations:

Simulation and Verification

Thoroughly simulating and verifying clock-related issues using appropriate tools and methodologies. Simulation helps identify potential problems early in the design process, allowing for timely corrections.

Design for Testability (DFT)

Incorporating clock-related test points and structures for efficient fault diagnosis. DFT techniques such as scan chains and built-in self-test (BIST) can be used to test clock networks and ensure their reliability.

Timing Closure

Ensuring timing closure by carefully analyzing setup and hold times, slack, and other timing parameters. Timing closure is essential for ensuring that the design meets all timing constraints and operates reliably.

Iterative Design Process

Refining clocking strategies through multiple design iterations and measurements. An iterative approach allows designers to fine-tune the clock network and achieve optimal performance.

Conclusion

Mastering advanced clocking techniques is essential for achieving optimal performance in high-speed FPGA designs. By carefully considering clock distribution, PLL design, clock gating, CTS, and low-power strategies, engineers can significantly improve system performance, reduce power consumption, and enhance design reliability. Continuous learning and adaptation to emerging technologies are crucial for staying ahead in this fast-paced field.

Advanced clocking techniques are vital for pushing the boundaries of FPGA performance. By understanding and implementing these strategies, engineers can create designs that not only meet but exceed the stringent demands of modern high-speed applications. Embrace the challenges and opportunities presented by advanced clocking to drive innovation and excellence in your FPGA projects.

Hire the Best Engineers with RunTime

At RunTime, we are dedicated to helping you find the best Engineering talent for your recruitment needs. Our team consists of engineers-turned-recruiters with an extensive network and a focus on quality. By partnering with us, you will have access to great engineering talent that drives innovation and excellence in your projects.

Discover how RunTime has helped 423+ tech companies find highly qualified and talented engineers to enhance their team’s capabilities and achieve strategic goals.

On the other hand, if you’re a control systems engineer looking for new opportunities, RunTime Recruitment’s job site is the perfect place to find job vacancies.