Achieving peak performance and reliability in high-frequency circuits demands a keen focus on combatting parasitic inductance and capacitance. These hidden circuit elements wield the power to disrupt signal integrity and efficiency, posing significant obstacles in electronics. Inductors and capacitors, vital building blocks of circuitry, harbor inherent parasitic properties that can wreak havoc if left unchecked.

Engineers tackle this issue through meticulous design layouts, precise component choices, and the strategic application of shielding methods to neutralize unwanted effects. By mastering the origins and consequences of parasitic elements, professionals can deploy robust solutions to curtail their influence and elevate the effectiveness of high-frequency circuits.

This exploration navigates the intricate landscape of combating parasitic characteristics within circuit designs, shedding light on effective strategies to optimize circuit performance.

Understanding Parasitic Effects

Impact of Parasitic Inductance and Capacitance on Circuit Behavior

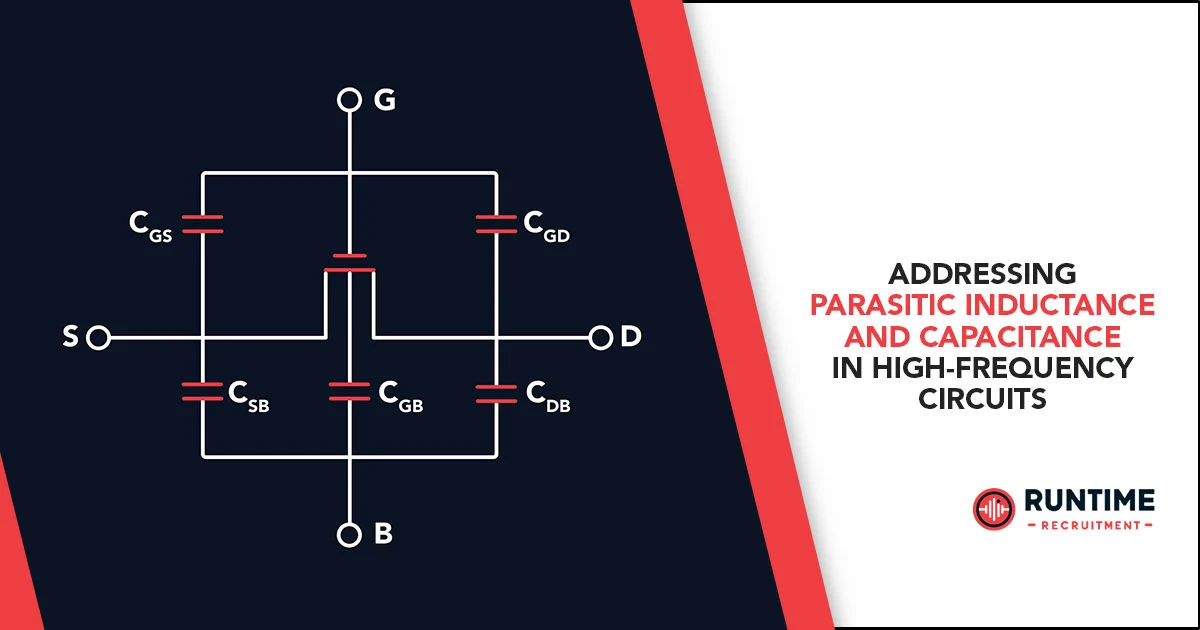

Parasitic inductance and capacitance are common occurrences in electronic circuits that can significantly affect the overall performance. Understanding how these parasitic elements impact circuit behavior is crucial for designing reliable and efficient circuits. Inductors and capacitors in a circuit exhibit parasitic properties due to factors such as the physical construction of components and the layout of the circuit itself.

Relationship Between Parasitic Effects and High-Frequency Circuits

In high-frequency circuits, the effects of parasitic inductance and capacitance become even more pronounced. The presence of parasitic elements can lead to unwanted resonances, impedance mismatches, signal distortion, and reduced bandwidth. These issues can degrade the circuit’s performance and even lead to malfunctions in critical applications. Designers of high-frequency circuits need to carefully consider and mitigate the impact of parasitic effects to ensure proper functionality and performance.

Strategies to Minimize Parasitic Effects

To minimize the impact of parasitic inductance and capacitance, several strategies can be employed during the circuit design phase. One approach is to optimize component placement and routing to reduce the length of traces and minimize loop areas, thereby decreasing parasitic inductance. Additionally, using low-inductance capacitors and high-frequency ceramic capacitors can help mitigate parasitic capacitance effects. Furthermore, employing techniques such as shielding, impedance matching, and proper grounding can aid in reducing the impact of parasitic elements in high-frequency circuits.

Importance of Simulation and Testing

Simulation tools play a vital role in identifying and analyzing parasitic effects in circuits. By simulating circuit performance under different conditions, designers can anticipate and address potential issues related to parasitic inductance and capacitance. Moreover, testing prototypes and evaluating circuit behavior in real-world scenarios are essential steps to validate the effectiveness of the design modifications aimed at mitigating parasitic effects. Through comprehensive simulation and testing procedures, designers can ensure the reliability and performance of high-frequency circuits in the presence of parasitic elements.

Common Applications Affected by Parasitic Effects

Parasitic inductance and capacitance are not limited to high-frequency circuits but can also impact various other electronic systems. For example, in power electronics, parasitic effects can lead to voltage spikes, electromagnetic interference, and decreased efficiency. Similarly, in analog circuits, parasitic elements can introduce noise, distortion, and instability. Understanding the implications of parasitic effects in different applications is essential for designing robust and reliable systems.

Future Trends in Mitigating Parasitic Effects

As electronic systems continue to evolve and operate at higher frequencies, the need to address parasitic effects becomes increasingly critical. Future trends in mitigating parasitic effects may involve advancements in materials science to develop components with reduced parasitic properties. Additionally, enhanced simulation tools capable of accurately modeling complex parasitic interactions could aid designers in implementing more effective mitigation strategies. Collaborative research efforts among industry experts and academia may pave the way for innovative solutions to combat parasitic effects and enhance the performance of electronic systems.

Common Challenges Faced

Identifying and Quantifying Parasitic Elements in Designs

In the realm of electronic design, engineers encounter a myriad of challenges, with one of the most prevalent being the presence of parasitic elements. These hidden components, including resistors, capacitors, and inductors, can clandestinely infiltrate a circuit, often stemming from factors like stray capacitance, lead inductance, and substrate resistance. A fundamental task for engineers is not only recognizing these parasitic elements but also accurately quantifying their impact on circuit performance. The ability to discern and measure these elements is paramount in crafting circuits that exhibit optimal functionality and efficiency.

Strategies for Identifying Parasitic Elements

To combat the adverse effects of parasitic elements, engineers employ a variety of techniques. Simulation tools play a pivotal role in modeling and simulating the behavior of these elements within a circuit. Moreover, approaches like frequency response analysis and impedance spectroscopy prove invaluable in pinpointing parasitic elements and evaluating their influence on circuit operations. By utilizing these methodologies, engineers can deepen their comprehension of parasitic effects within their designs.

Mitigating Parasitic Elements Without Compromising Performance

Following the identification of parasitic elements, engineers embark on the challenge of diminishing their impact without sacrificing circuit efficiency. This delicate balance necessitates thoughtful strategies and innovative solutions. Engineers frequently turn to design optimizations, layout adjustments, and the integration of decoupling capacitors or inductors to counteract the repercussions of parasitic elements. Through strategic implementation of these measures, engineers can curtail the adverse effects of parasitics while enhancing overall circuit performance.

Overcoming the Hurdles

While the obstacles presented by parasitic elements are substantial, they are far from insurmountable. By augmenting their comprehension of these elements, leveraging advanced simulation tools, and implementing effective mitigation strategies, engineers can conquer these challenges and fashion resilient, high-performance electronic circuits. Vigilance and proactivity are essential traits for design engineers, ensuring the dependability and functionality of electronic designs amidst the pervasive presence of parasitic elements.

Techniques for Mitigating Parasitic Effects

Parasitic effects are unwanted elements that can degrade the performance of electronic circuits. In order to ensure optimal functionality and reliability, it is crucial to implement techniques that mitigate these parasitic effects. This blog section will discuss several effective strategies for minimizing parasitic inductance and capacitance, optimizing the use of decoupling components, and grounding techniques to reduce unwanted effects. By following these techniques, designers can enhance the overall performance of their electronic systems.

Optimizing Layout and Routing for Reduced Parasitic Inductance and Capacitance

Proper layout and routing of electronic components can significantly impact the level of parasitic inductance and capacitance in a circuit. By carefully designing the layout and routing of traces, loops, and components, designers can minimize unwanted parasitic effects. Techniques such as shortening trace lengths, avoiding sharp corners, and optimizing component placement can help reduce parasitic inductance and capacitance.

Effective Use of Decoupling Capacitors and Inductors

Decoupling capacitors and inductors play a crucial role in mitigating parasitic effects in electronic circuits. By strategically placing decoupling components near sensitive devices, designers can filter out noise and provide stable power distribution. Selecting the appropriate capacitance and inductance values, as well as considering the frequency response of the components, is essential for effective parasitic mitigation.

Grounding Strategies to Minimize Parasitic Effects

Proper grounding is essential for reducing parasitic effects in electronic circuits. By implementing a solid grounding scheme, designers can minimize ground loops, reduce noise, and improve signal integrity. Techniques such as star grounding, grounding planes, and separating analog and digital grounds can help mitigate parasitic effects related to ground connections.

Shielding Techniques for Parasitic Reduction

In addition to layout optimization and decoupling components, shielding techniques can further mitigate parasitic effects. Shielding sensitive components or signals from external interference sources such as electromagnetic fields or radio frequency signals can significantly improve circuit performance. Employing conductive enclosures, grounded shields, and twisted pair wiring are common shielding practices that can effectively reduce parasitic influences.

Simulation and Analysis Tools for Parasitic Evaluation

Utilizing simulation and analysis tools can aid in evaluating and mitigating parasitic effects during the design phase. Software tools like SPICE simulations, electromagnetic field solvers, and signal integrity analysis software can help identify potential parasitic issues before prototyping. By simulating the circuit behavior under different conditions, designers can optimize the layout, component selection, and grounding schemes to minimize parasitic effects.

By employing the discussed techniques for mitigating parasitic effects, designers can enhance the performance and reliability of their electronic systems. Understanding the impact of parasitic inductance and capacitance, utilizing decoupling components effectively, implementing proper grounding strategies, incorporating shielding techniques, and leveraging simulation tools are essential steps in optimizing circuit performance and minimizing unwanted effects.

Advanced Solutions in High-Frequency Circuits

In the realm of high-frequency circuits, where signals oscillate at rapid rates, the significance of advanced solutions cannot be overstated. Engineers and designers are constantly pushing the boundaries of innovation to enhance performance, minimize losses, and optimize efficiency. This blog section delves into some key strategies and methodologies that are revolutionizing high-frequency circuit design.

Utilizing Distributed Capacitance and Inductance Models for Improved Designs

One of the fundamental challenges in high-frequency circuits is managing parasitic elements such as stray capacitance and inductance. These unwanted elements can significantly impact circuit performance, leading to signal distortion and loss. To address this issue, engineers are increasingly turning to distributed capacitance and inductance models. By strategically incorporating these models into their designs, engineers can minimize the impact of parasitic elements, resulting in improved signal integrity and overall circuit performance.

Role of Simulation Tools in Predicting and Managing Parasitic Elements

Simulation tools play a crucial role in the design and optimization of high-frequency circuits. They enable engineers to predict the behavior of complex circuits, identify potential issues related to parasitic elements, and fine-tune designs before physical implementation. By leveraging advanced simulation tools, engineers can gain valuable insights into the behavior of their circuits, allowing them to make informed decisions and optimize performance. In the realm of high-frequency circuits, simulation tools are indispensable for predicting and managing parasitic elements effectively.

Innovative Approaches to Tackle Parasitic Effects

As high-frequency circuits continue to evolve, innovative approaches are being developed to tackle parasitic effects. From advanced packaging techniques to novel material technologies, engineers are exploring a wide range of solutions to mitigate the impact of parasitic elements. By thinking outside the box and adopting unconventional strategies, designers can overcome traditional limitations and achieve breakthroughs in high-frequency circuit design.

The Importance of Impedance Matching in High-Frequency Circuits

Impedance matching is a critical aspect of high-frequency circuit design that directly influences signal transfer efficiency and power delivery. Engineers must carefully tune impedance levels to ensure maximum power transfer between components and minimize signal reflections. Failure to achieve proper impedance matching can result in signal distortion, reduced efficiency, and even damage to circuit components. By implementing impedance matching techniques, engineers can optimize circuit performance and enhance overall system reliability.

Emerging Trends in High-Frequency Circuit Design

The field of high-frequency circuit design is continuously evolving, driven by technological advancements and industry demands. Some emerging trends include the integration of artificial intelligence for automated design optimization, the development of compact and efficient RF components for wireless communication systems, and the increasing focus on energy-efficient circuitry for IoT applications. By staying abreast of these trends and embracing innovative design practices, engineers can stay ahead of the curve and deliver cutting-edge solutions in high-frequency circuit design.

Advanced solutions are reshaping the landscape of high-frequency circuits, offering new possibilities and opportunities for innovation. By embracing distributed capacitance and inductance models, leveraging simulation tools, exploring innovative approaches, emphasizing impedance matching, and keeping up with emerging trends, engineers can unlock the full potential of high-frequency circuit design and pave the way for future advancements in the field.

Real-World Applications and Success Stories

Effective Strategies for Parasitic Reduction in Electronic Circuits

• Optimizing PCB Layout for Reduced Parasitic Capacitance

• Shielding Techniques to Minimize Parasitic Resistance

Benefits of Implementing Proper Parasitic Management

• Enhanced Signal Integrity and Reduced Crosstalk

• Improved Power Efficiency and Heat Dissipation

• Increased Reliability and Longevity of Electronic Systems

• Cost Savings through Lower Failure Rates and Maintenance Expenses

Real-world applications demonstrate the critical role of effective parasitic reduction techniques in optimizing circuit performance and reliability. By strategically addressing parasitic elements like capacitance, resistance, and inductance, engineers can significantly enhance the functionality and efficiency of electronic systems. The success stories presented in this section underscore the importance of proactive parasitic management in overcoming design challenges and achieving superior circuit performance. Moreover, the tangible benefits of mitigating parasitic effects extend beyond performance enhancements to include cost savings and increased product lifespan. Embracing best practices in parasitic reduction is essential for engineers and designers seeking to deliver high-quality, robust electronic solutions in today’s competitive market.

Exploring Advanced Parasitic Reduction Techniques

• Implementing 3D EM Simulations for Precise Parasitic Analysis

• Integration of Active Noise Cancellation for Parasitic Interference Control

In the realm of electronic design, cutting-edge technologies have revolutionized the approach to parasitic reduction. Engineers are now leveraging advanced tools like 3D electromagnetic simulations to gain a deeper understanding of parasitic effects and optimize circuit layouts with unparalleled accuracy. Additionally, the integration of active noise cancellation mechanisms has proven instrumental in combating parasitic interference, ensuring optimal signal integrity and performance stability in complex electronic systems.

Driving Innovation with Adaptive Parasitic Control

• Dynamic Parasitic Monitoring Systems for Real-Time Adjustment

• Machine Learning Algorithms for Adaptive Parasitic Mitigation

The future of parasitic management lies in adaptive control strategies that can dynamically respond to changing operational conditions and environmental factors. Real-time monitoring systems equipped with intelligent algorithms enable automatic adjustments to mitigate parasitic issues as they arise, fostering a proactive approach to circuit optimization and reliability. Machine learning algorithms further enhance this capability by continuously learning from system behavior and implementing adaptive parasitic mitigation measures, paving the way for unprecedented levels of performance efficiency and resilience in electronic designs.

Future Trends in Parasitic Management

In the realm of electronic design and engineering, the management of parasitic elements like inductance and capacitance is critical to ensure optimal performance of devices and systems. As technology advances, the need for effective strategies to combat parasitic effects becomes increasingly important. Let’s delve into some of the future trends shaping this domain.

Emerging Technologies for Combating Parasitic Inductance and Capacitance

One of the key areas of focus in parasitic management is the development of innovative technologies that can effectively minimize the impact of parasitic elements. Engineers are exploring novel approaches such as advanced materials with tailored properties to reduce inductance and capacitance in circuits. Additionally, the integration of machine learning algorithms for predictive modeling of parasitic effects shows great promise in optimizing circuit designs. Furthermore, the utilization of nanotechnology in creating specialized components with reduced parasitic effects is gaining traction in the industry.

Challenges in Mitigating Parasitic Effects at Higher Frequencies

As electronic devices operate at higher frequencies, the challenges associated with mitigating parasitic effects escalate. The interactions between components become more complex, leading to increased parasitic inductance and capacitance. Engineers are faced with the task of designing robust solutions that can handle these challenges effectively. Moreover, the implementation of advanced signal processing techniques and adaptive filtering methods is being explored to counteract the impact of parasitic elements at higher frequencies. Additionally, the emergence of 5G technologies and the Internet of Things (IoT) further complicate the landscape, requiring innovative strategies to manage parasitic effects in next-generation electronic systems.

Looking ahead, the field of parasitic management is poised for significant advancements driven by continuous innovation and collaboration across disciplines. By staying abreast of emerging technologies and addressing the challenges posed by higher frequencies, engineers can pave the way for more efficient and reliable electronic designs. The integration of interdisciplinary research efforts, including collaborations with material scientists, physicists, and computer engineers, will be instrumental in pushing the boundaries of parasitic management and enhancing the performance of future electronic systems.

Conclusion

Managing parasitic inductance and capacitance in high-frequency circuits is crucial for maintaining signal integrity and ensuring optimal circuit performance. By employing proper layout techniques, component selection, and impedance matching, designers can effectively mitigate the effects of parasitic elements. It is essential to understand the impact of parasitic inductance and capacitance on circuit behavior and take proactive measures to minimize their adverse effects. With careful consideration and strategic design practices, high-frequency circuits can achieve the desired performance levels and meet the stringent requirements of modern electronic applications.