Dynamic Partial Reconfiguration (DPR) is an advanced FPGA technique that allows for the modification of specific FPGA blocks while the device is operational. This capability offers significant advantages in terms of flexibility, resource utilization, and adaptability, making it a compelling option for a wide range of applications. However, implementing DPR effectively requires a deep understanding of FPGA architecture, design methodologies, and the specific tools provided by FPGA vendors. This deep dive aims to demystify DPR and provide a comprehensive guide to its practical implementation.

Understanding the Basics

Before delving into the practical aspects of DPR, it’s essential to grasp the fundamental concepts:

- Partial Reconfiguration: The ability to reconfigure a portion of the FPGA without affecting the rest of the device. This allows for updating certain functionalities while keeping the system running.

- Dynamic Reconfiguration: The reconfiguration occurs while the FPGA is actively processing data, enabling real-time system updates and modifications.

- Partially Reconfigurable Module (PRM): A discrete functional unit designed to be dynamically reconfigured. PRMs can be swapped in and out as needed, adding to the system’s versatility.

- Static Region: The portion of the FPGA that remains unchanged throughout the device’s operation. It typically contains the critical control logic and interfaces necessary for system stability.

Understanding these basics sets the foundation for exploring more complex DPR implementations and leveraging its full potential.

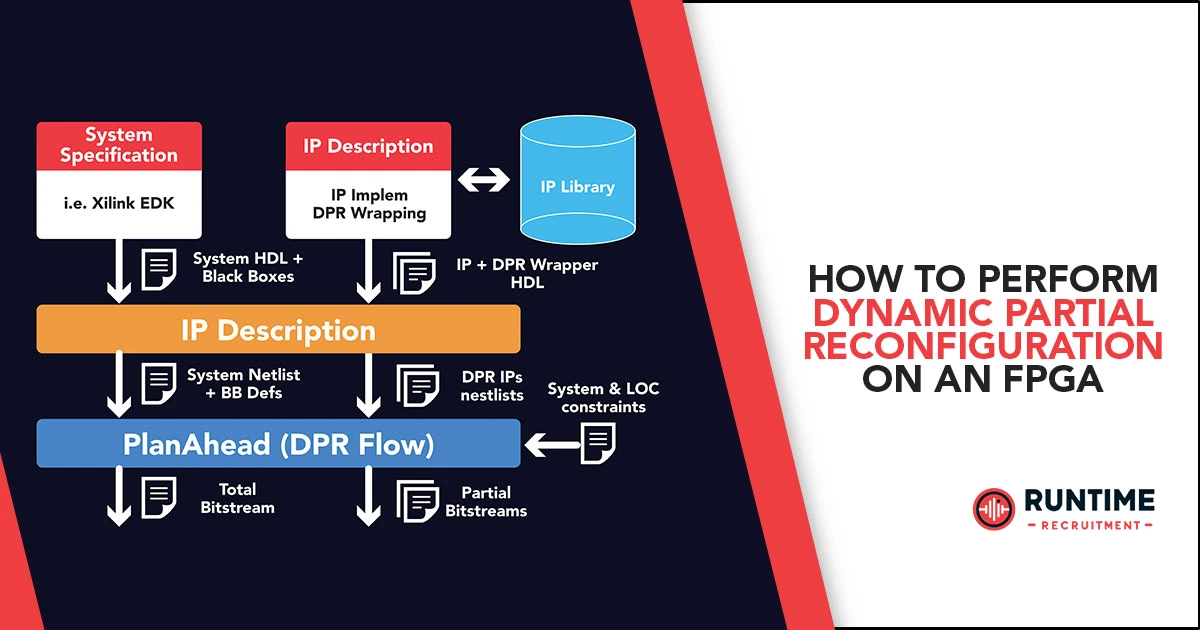

Design Methodology and Tool Flow

Effective DPR implementation necessitates a well-structured design methodology. Consider the following steps:

- Design Partitioning: Divide the FPGA design into static and dynamic regions. The static region houses critical control logic and interfaces, while the dynamic region accommodates PRMs. This partitioning is crucial for maintaining system stability during reconfiguration.

- PRM Development: Create modular PRMs with clear interfaces to facilitate seamless integration and reconfiguration. Each PRM should be designed to perform a specific function and be easily interchangeable.

- Bitstream Generation: Generate partial bitstreams for each PRM using the FPGA vendor’s tools. These bitstreams contain the configuration data for the corresponding PRMs. Efficient bitstream generation is essential for minimizing reconfiguration time.

- Reconfiguration Management: Develop a mechanism to manage the reconfiguration process, including bitstream loading, timing constraints, and error handling. This management system ensures smooth transitions and system reliability.

Following a systematic design methodology and utilizing the right tools can significantly enhance the effectiveness of DPR.

Key Challenges and Considerations

However, DPR is not without its challenges:

- Reconfiguration Overhead: The time required to reconfigure a PRM can impact system performance. Careful optimization is crucial to minimize this overhead and maintain efficiency.

- Design Complexity: Managing multiple design states and ensuring correct functionality during transitions requires meticulous planning and thorough testing.

- Tool Limitations: Not all FPGA vendors provide comprehensive DPR support, and tool maturity can vary. It is important to choose tools that best fit the specific requirements of your design.

- Power Consumption: Reconfiguration can introduce additional power consumption due to configuration data transfer and state changes. Power management strategies must be implemented to address this.

Addressing these challenges proactively can lead to more robust and efficient DPR implementations.

Practical Implementation and Optimization

To optimize DPR performance and efficiency, consider the following strategies:

- Overlapping Reconfiguration: Initiate the reconfiguration process for the next PRM while the current one is still operational, reducing idle time and improving overall system throughput.

- Reconfiguration Time Minimization: Optimize bitstream size and loading algorithms to minimize reconfiguration latency. Smaller bitstreams and efficient loading processes can significantly enhance reconfiguration speed.

- Design for Reconfigurability: Adopt modular design principles and use hierarchical design structures to facilitate PRM creation and management. Modular designs are easier to manage and reconfigure.

- Thorough Verification: Rigorous testing is essential to ensure correct functionality under various reconfiguration scenarios. Comprehensive verification helps identify and mitigate potential issues early in the design process.

Implementing these strategies can lead to more efficient and reliable DPR systems.

Advanced Topics

For those seeking to push the boundaries of DPR, explore these areas:

- Self-Reconfigurable Systems: Develop systems capable of autonomously adapting their configuration based on runtime conditions. This can lead to highly adaptable and resilient systems.

- Hardware/Software Co-Design: Integrate DPR with software-based reconfiguration for enhanced flexibility. Combining hardware and software reconfiguration can offer greater control and optimization opportunities.

- DPR for Fault Tolerance: Utilize DPR to mitigate the effects of hardware failures by dynamically replacing faulty components. This approach can significantly enhance system reliability and lifespan.

Exploring these advanced topics can lead to innovative applications and further enhance the capabilities of DPR.

Conclusion

Dynamic Partial Reconfiguration offers immense potential for improving FPGA system adaptability and resource utilization. By carefully considering design methodologies, optimization techniques, and potential challenges, engineers can harness the power of DPR to create innovative and efficient solutions. The ability to dynamically adapt to changing requirements in real-time makes DPR an invaluable tool in the FPGA designer’s arsenal.