As field engineers, we understand the critical role data integrity plays in FPGA-based communication systems. Even a single-bit error during transmission can wreak havoc on downstream processes. This article delves into the practical implementation of Error Correction Codes (ECC) for robust data transmission within FPGA communication channels. We’ll explore various ECC techniques, analyze their trade-offs, and delve into innovative implementation strategies specifically suited for FPGA architectures.

Understanding the ECC Landscape

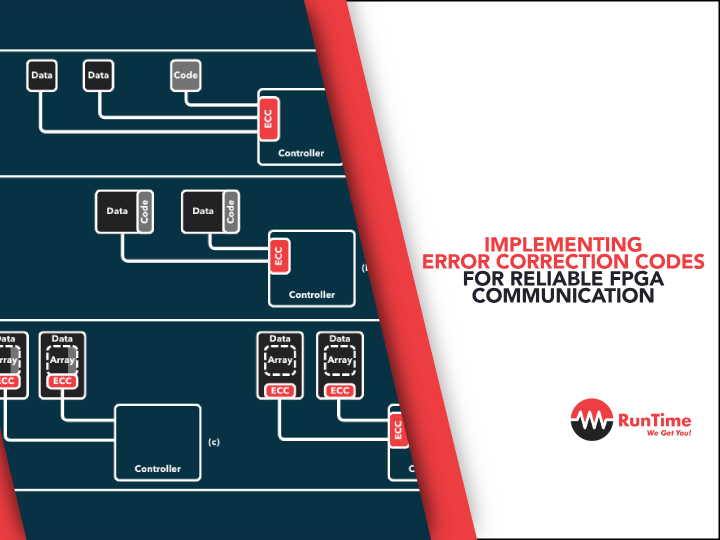

ECC schemes add redundant information to the original data stream, enabling the receiver to detect and potentially correct errors introduced during transmission. The choice of ECC algorithm hinges on several factors, including:

Error Correction Capability

This refers to the number of errors an ECC code can rectify within a codeword (data + ECC bits). Single-Error Correcting (SEC) codes are widely used, but for scenarios with higher noise levels, Double-Error Correcting (DEC) codes might be necessary. The error correction capability is crucial in determining how resilient the communication system will be against data corruption. For instance, SEC codes can correct single-bit errors effectively, making them suitable for relatively clean communication environments. In contrast, DEC codes can handle two-bit errors, providing additional robustness for noisier channels.

Overhead

The additional bits introduced by the ECC scheme reduce data payload efficiency. Selecting the optimal balance between error correction capability and overhead is crucial. High overhead can lead to reduced effective data rates, which might not be acceptable in bandwidth-constrained applications. For example, Hamming codes add a modest amount of overhead, making them efficient for many applications, whereas Reed-Solomon codes introduce more significant overhead but offer superior error correction.

Implementation Complexity

Different ECC algorithms have varying hardware resource requirements within the FPGA. For resource-constrained applications, simpler codes might be preferred. Implementation complexity impacts the design’s feasibility and performance. Hamming codes, for instance, are relatively simple to implement and require minimal hardware resources, while Low-Density Parity-Check (LDPC) codes, despite their excellent error correction capabilities, can be more complex and resource-intensive to implement.

Common ECC Techniques Employed in FPGA Communication

Hamming Codes

Hamming codes provide a good balance between error correction capability, overhead, and implementation complexity. They can detect and correct single-bit errors within a codeword, making them ideal for systems where single-bit errors are the most common type of corruption. Their simplicity and efficiency make them a popular choice in many FPGA-based communication systems.

Reed-Solomon (RS) Codes

Offering powerful error correction capabilities, RS codes are well-suited for scenarios with high burst error rates. They can correct multiple errors within a codeword, making them highly effective in environments with frequent and clustered errors. However, they come with increased decoding complexity, requiring more sophisticated hardware and processing power.

Low-Density Parity-Check (LDPC) Codes

LDPC codes provide excellent error correction performance with moderate decoding complexity. They are particularly effective in applications requiring high reliability, such as digital television and data storage systems. However, their irregular structure can pose challenges for efficient FPGA implementation, necessitating careful design to optimize resource usage.

Innovation at the Forefront: FPGA-Specific ECC Implementations

Beyond the standard ECC algorithms, let’s explore some innovative approaches tailored for FPGAs:

Pipeline Architectures

By pipelining the encoding and decoding processes, we can achieve higher throughput and reduce latency. This approach leverages the inherent parallelism of FPGAs, enabling the system to handle multiple stages of processing concurrently. Pipeline architectures are particularly beneficial in high-speed communication systems where minimizing latency is critical.

Soft-Decision Decoding

Traditional ECC operates on hard-decision bits (0 or 1). However, FPGAs can exploit the signal quality information from the channel to improve decoding performance through soft-decision decoding algorithms. This technique uses probabilistic information about the received signals to enhance error correction, leading to better performance in noisy environments.

Custom Code Design

For specific applications with well-defined error profiles, it might be beneficial to explore custom code designs. This can lead to optimized hardware utilization and potentially superior error correction capabilities compared to off-the-shelf solutions. Custom codes can be tailored to the unique characteristics of the communication channel, providing enhanced performance and efficiency.

Analytical Evaluation: Choosing the Right ECC for Your Application

When selecting an ECC scheme for your FPGA communication system, a thorough analytical approach is essential. Here’s a breakdown of key considerations:

Channel Characteristics

Analyze the expected error rate and error burst length of your communication channel. This will guide the selection of an ECC code with the appropriate correction capability. Understanding the channel’s behavior helps in choosing an ECC scheme that effectively mitigates the most likely types of errors.

FPGA Resource Constraints

Evaluate the available hardware resources within your FPGA, including logic elements, block RAMs, and DSP slices. This will determine the feasibility of implementing more complex ECC algorithms. Ensuring that the chosen ECC code fits within the FPGA’s resource limits is crucial for successful implementation.

Performance Requirements

Consider the desired data throughput and latency of your communication system. Pipeline architectures and efficient decoding algorithms can help meet these requirements. High-performance systems often require ECC schemes that provide robust error correction without compromising speed.

By carefully evaluating these factors, you can make an informed decision on the most suitable ECC scheme for your specific FPGA application. A well-chosen ECC scheme enhances the reliability and efficiency of the communication system, ensuring robust data transmission even in the presence of errors.

Conclusion

Implementing robust ECC schemes within FPGA communication channels is paramount for ensuring data integrity. This article has provided a technical deep dive, exploring various ECC algorithms, innovative FPGA-specific implementation strategies, and analytical considerations for choosing the optimal solution. Remember, the success hinges on carefully balancing error correction capability, overhead, and implementation complexity within the context of your unique application.

The journey from understanding ECC fundamentals to implementing them on FPGAs involves multiple considerations, including the nature of the communication channel, available FPGA resources, and performance requirements. By leveraging the flexibility and power of FPGAs, engineers can design communication systems that are both reliable and efficient. As technology advances, mastering ECC implementation will remain a critical skill for ensuring the robustness of digital communication systems. By following the guidelines provided in this article, you can confidently navigate the complexities of ECC implementation, achieving reliable and high-performance communication in your FPGA-based systems.

Hire the Best Engineers with RunTime

At RunTime, we are dedicated to helping you find the best Engineering talent for your recruitment needs. Our team consists of engineers-turned-recruiters with an extensive network and a focus on quality. By partnering with us, you will have access to great engineering talent that drives innovation and excellence in your projects.

Discover how RunTime has helped 423+ tech companies find highly qualified and talented engineers to enhance their team’s capabilities and achieve strategic goals.

On the other hand, if you’re a control systems engineer looking for new opportunities, RunTime Recruitment’s job site is the perfect place to find job vacancies.