Finite State Machines (FSMs) are essential in digital design as they provide a structured approach to modeling and controlling sequential logic. Field-Programmable Gate Arrays (FPGAs) are versatile hardware platforms that can be programmed to implement custom digital circuits. Therefore, FSMs are widely used in FPGA designs.

This article aims to guide you through the process of designing and implementing FSMs on an FPGA using Verilog or VHDL, which are two of the most popular hardware description languages.

Understanding Finite State Machines

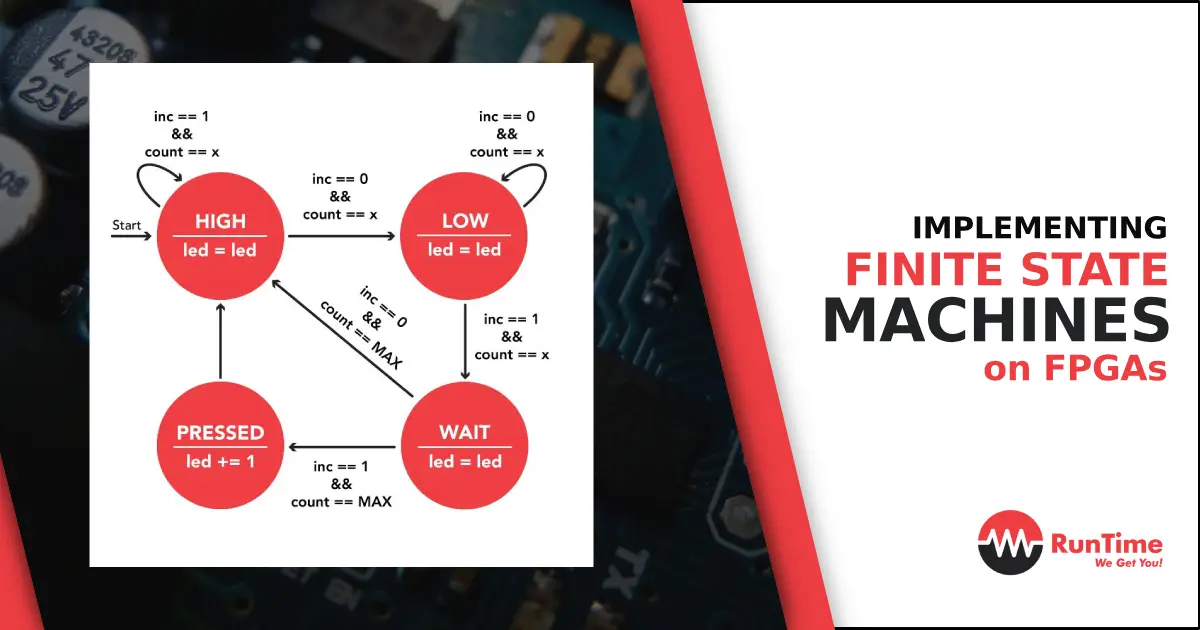

Before delving into the implementation, let’s briefly revisit the concept of FSMs. FSMs consist of a set of states, transitions between these states, and actions associated with transitions. These machines are invaluable for modeling systems with distinct operational modes and are widely used in applications ranging from digital controllers to communication protocols.

How to Implement Finite State Machines

Step 1: Define States and Inputs/Outputs

In defining states, consider the granularity required for your specific application. States represent the different operating modes of your system, and selecting them appropriately is crucial. Ensure that input and output signals are clearly defined, specifying the conditions that trigger state transitions and the corresponding outputs associated with each state.

Step 2: Design the State Diagram

Elaborate on the state diagram creation process. Use tools like draw.io or specialized software like StateCAD to visualize state transitions. Clearly label transitions with associated input conditions and actions. This diagram serves as a communication tool for stakeholders and aids in collaborative design efforts.

Step 3: Code the FSM in Verilog/VHDL

Expand on the code structure by incorporating best practices. Implementing a modular design enhances code readability and facilitates easier maintenance. Use separate modules for the state machine, state register, next-state logic, and output logic. This modularity simplifies debugging and allows for easy modifications or expansions in the future.

Additionally, consider using enumerated types in VHDL for better code clarity. Enumerated types can improve the readability of your code by providing meaningful names to state values.

Step 4: Simulate the FSM

In the simulation phase, conduct a thorough analysis of the FSM’s behavior. Explore corner cases and edge scenarios to ensure the robustness of your design. Utilize waveform viewers to inspect signal transitions and verify that the FSM behaves as expected. Consider creating assertions within your testbench to automatically detect violations of expected behavior.

Step 5: Synthesize and Implement on FPGA

During synthesis, be mindful of the target FPGA’s resources and constraints. Optimization is key to achieving a balance between performance and resource utilization. Utilize synthesis reports to analyze critical paths, identify potential bottlenecks, and make informed optimizations. Take advantage of vendor-specific optimizations and constraints to tailor your design to the capabilities of the chosen FPGA.

Advanced Considerations

- Parallelism: Explore opportunities for parallelism within your FSM design. Parallel execution of certain tasks can improve overall system performance.

- Power Optimization: Depending on your application, power consumption may be a critical consideration. Investigate power optimization techniques provided by FPGA vendors to minimize energy usage.

- State Encoding: Experiment with different state encoding schemes to optimize the usage of flip-flops in your design. Gray coding or one-hot encoding may provide benefits in terms of reduced logic complexity and improved speed.

- FSM Hierarchy: For complex systems, consider using a hierarchical FSM design. Divide the FSM into smaller, manageable modules, each responsible for a specific aspect of the overall system behavior. This approach simplifies design, debugging, and maintenance.

Conclusion

Designing Finite State Machines (FSMs) for Field Programmable Gate Arrays (FPGAs) requires a comprehensive approach that goes beyond coding. Taking into account additional considerations can help you create a more advanced and optimized FSM design. As FPGA technology is constantly evolving, staying up-to-date with the latest tools and methodologies will enable you to develop efficient and reliable digital systems.

Hire the Best Engineers with RunTime Recruitment

If you’re searching for highly skilled engineers worldwide, our expert team of engineers-turned-recruiters is here to help you. We offer in-depth knowledge of technical recruiting in the engineering industry to make the sourcing process much easier for you.

On the other hand, if you’re an engineer looking for new opportunities, RunTime Recruitment’s job site is the perfect place to find job vacancies.