# Parallel Processing Paradigms

# Transputer Architectures for Engineers

Lance Harvie Bsc (Hons)

# **Table Of Contents**

| Chapter 1: Introduction to Transputer Architectures     | 3  |

|---------------------------------------------------------|----|

| Overview of Transputer Technology                       | 3  |

| Historical Context and Development                      | 5  |

| Importance of Transputers in Modern Engineering         | 7  |

| Chapter 2: Fundamentals of Parallel Processing          | 9  |

| Principles of Parallel Processing                       | 9  |

| Types of Parallelism                                    | 11 |

| Benefits and Challenges of Parallel Processing          | 13 |

| Chapter 3: Transputer Architecture                      | 15 |

| Core Components of Transputers                          | 15 |

| Communication Protocols in Transputers                  | 16 |

| Programming Models for Transputers                      | 18 |

| Chapter 4: Transputers in Parallel Processing           | 20 |

| Case Studies of Parallel Processing Applications        | 20 |

| Transputers vs. Traditional Processing Architectures    | 22 |

| Performance Metrics for Transputer Systems              | 23 |

| Chapter 5: Design Considerations for Transputer Systems | 26 |

| System Architecture Design                              | 26 |

| Resource Management and Allocation                      | 27 |

| Fault Tolerance in Transputer Systems                   | 28 |

| Chapter 6: Transputers in Embedded Systems              | 31 |

| Role of Transputers in Embedded Applications            | 31 |

| Integration with Other Embedded Components              | 33 |

| Real-Time Processing with Transputers                   | 34 |

| Chapter 7: Programming Transputers                 | 37 |

|----------------------------------------------------|----|

| Overview of Programming Languages for Transputers  | 37 |

| Developing Efficient Parallel Algorithms           | 39 |

| Debugging and Optimization Techniques              | 41 |

| Chapter 8: Future Trends in Transputer Technology  | 43 |

| Emerging Applications and Innovations              | 43 |

| Evolution of Transputer Design                     | 45 |

| The Role of Transputers in AI and Machine Learning | 46 |

| Chapter 9: Conclusion and Final Thoughts           | 49 |

| Recap of Key Concepts                              | 49 |

| The Future of Transputer Architectures             | 50 |

| Call to Action for Engineers and Managers          | 52 |

# Chapter 1: Introduction to Transputer Architectures

## **Overview of Transputer Technology**

Transputer technology emerged in the 1980s as a revolutionary approach to parallel processing, designed to facilitate high-performance computing tasks while simplifying the complexities associated with traditional architectures. At its core, a transputer is a microprocessor that integrates processing, communication, and memory capabilities into a single

unit, allowing multiple transputers to be connected in a network. This architecture enables efficient data transfer and processing across various nodes, making it particularly suitable for applications requiring high throughput and low latency. The inherent parallelism offered by transputers allows engineers to design systems that can handle complex computations and real-time data processing with remarkable efficiency.

One of the defining features of transputer technology is its unique communication model, which employs a point-to-point connection scheme among processors. Each transputer can communicate directly with its neighbors using a lightweight message-passing protocol, which contrasts sharply with the shared memory systems prevalent in other architectures. This design not only minimizes bottlenecks but also enhances scalability, as engineers can easily add more transputers to a network without compromising performance. The modular nature of transputer systems allows for versatile configurations, making them ideal for various applications, from scientific simulations to industrial automation. Transputers have found significant applications in parallel processing environments where computational tasks can be divided among multiple processors. This capability is particularly beneficial in fields such as computational fluid dynamics, image processing, and artificial intelligence, where large data sets and complex algorithms demand considerable processing power. By leveraging the parallel execution capabilities of transputers, engineers can significantly reduce processing times and improve the overall efficiency of systems. Furthermore, the ability to reconfigure and program transputer networks enhances their adaptability to changing computational needs, making them a valuable asset in dynamic engineering environments.

In embedded systems, transputers offer a compelling solution for integrating parallel processing capabilities within constrained environments. Their compact design and low power consumption make them suitable for applications in robotics, telecommunications, and automotive systems, where space and energy efficiency are paramount. Bv embedding transputers into devices, engineers can enable sophisticated functionalities such as real-time data analysis, adaptive control systems, and enhanced communication protocols. This integration not only improves performance but also fosters innovation, allowing for the development of smarter, more capable embedded systems.

The evolution of transputer technology has paved the way for a broader understanding of parallel processing paradigms in engineering. As industries continue to demand higher performance and greater efficiency from their computational systems, the principles established by transputer architecture remain relevant. Engineers and engineering managers who embrace these paradigms can leverage the strengths of transputers to develop robust, scalable, and efficient solutions that meet the challenges of modern computing. Understanding the fundamental aspects of transputer technology is essential for professionals seeking to harness the full potential of parallel processing in their projects and applications.

#### **Historical Context and Development**

The historical context of transputer architecture is rooted in the evolution of parallel processing technologies that began in the 1960s. Early computers operated on a sequential processing model, which limited their performance and efficiency as tasks complexity. arew in Engineers and researchers sought ways to enhance

computational speed and resource utilization, leading to the exploration of parallel processing methods. The concept of dividing tasks among multiple processing units emerged as a viable solution to overcome the limitations of traditional architectures. This shift laid the groundwork for the development of the transputer, a specialized processor designed to facilitate parallel computation.

In the early 1980s, the introduction of the transputer by Inmos marked a significant milestone in computing history. The transputer was designed not only as a powerful processor but also as a communication hub, allowing multiple transputers to be interconnected in a network. This innovative design enabled engineers to create scalable systems

that could efficiently tackle complex computational problems. The transputer architecture was characterized by its unique features, including a simple instruction set, built-in communication capabilities, and a focus on parallel processing. These attributes distinguished it from conventional microprocessors and positioned it as a pioneering technology in the realm of embedded systems and parallel computing.

The development of the transputer architecture was heavily influenced by the increasing demand for high-performance computing in various engineering fields. Industries such as telecommunications, aerospace, and robotics required systems capable of processing large volumes of data in real-time. The transputer's ability to support multiple processing units working simultaneously allowed engineers to design sophisticated applications that could perform parallel tasks effectively. This capability was particularly advantageous in embedded systems, where computing resources are often limited, and efficiency is paramount. Engineers quickly recognized the potential of transputers to enhance performance in applications requiring rapid data processing and complex calculations.

Throughout the 1990s, the transputer architecture saw further advancements and adaptations. Researchers and engineers experimented with different configurations and programming models to optimize the performance of transputer-based systems. The introduction of software tools and languages specifically designed for parallel processing, such as Occam, enabled developers to harness the full potential of transputer networks. These tools simplified the programming of parallel applications, making it accessible to a broader range of engineers. As a result, transputers began to find applications beyond their initial scope, influencing the design of modern parallel processing systems and embedded solutions.

In recent years, the legacy of transputer architecture continues to resonate within the engineering community. While newer technologies have emerged, the principles established by transputers remain relevant in the design and implementation of parallel processing systems. Engineers and engineering managers are increasingly focused on developing efficient architectures that leverage parallelism to meet the demands of contemporary applications. The historical development of transputer technology serves as a foundational reference for understanding current trends in parallel processing and embedded systems, emphasizing the importance of innovative thinking in engineering practices.

#### Importance of Transputers in Modern Engineering

The transputer, a pioneering technology in parallel processing, has made significant contributions to modern engineering practices. This unique architecture, designed specifically for concurrent computation, allows engineers to tackle complex problems that require high levels of processing power and efficiency. By enabling multiple processes to run simultaneously, transputers facilitate advancements in various engineering fields, including robotics, telecommunications, and control systems, where real-time processing and responsiveness are critical.

One of the primary advantages of transputers lies in their intrinsic ability to handle parallel tasks. In traditional computing models, processing tasks are often executed sequentially, leading to bottlenecks and inefficiencies, especially in applications requiring substantial computational resources. The transputer's architecture, which supports multiple processing units interconnected via a high-speed network, allows engineers to distribute workloads effectively. This parallelism not only accelerates computation times but also enhances overall system performance, enabling engineers to solve larger and more intricate problems that were previously deemed infeasible.

Transputers also play a vital role in embedded systems, where resource constraints and real-time processing requirements are paramount. In embedded applications, such as automotive control systems or industrial automation, the ability to perform multiple operations concurrently is essential for maintaining system reliability and responsiveness. The modular nature of transputer designs allows for efficient scaling, making them ideal for embedded applications that require varying levels of processing power. Engineers can leverage this flexibility to create optimized solutions tailored to specific application needs, ensuring that systems remain efficient and effective. Moreover, the use of transputers promotes improved system reliability and fault tolerance. By distributing tasks across multiple processing units, transputers can isolate failures, preventing a single point of failure from compromising the entire system. This feature is particularly beneficial in mission-critical applications, such as aerospace and medical devices, where system integrity is non-negotiable. Engineers can design robust systems with built-in redundancies, leading to enhanced safety and operational reliability, which are crucial factors in engineering design and management.

In conclusion, the importance of transputers in modern engineering cannot be overstated. Their ability to support parallel processing and efficient task distribution has enabled engineers to innovate and refine their approaches to complex problems across various sectors. As industries continue to evolve and demand greater computational capabilities, transputers are poised to remain a cornerstone of engineering design and development. By embracing transputer architectures, engineers can push the boundaries of what is possible, driving advancements that will shape the future of technology and engineering practices.

# Chapter 2: Fundamentals of Parallel Processing

#### **Principles of Parallel Processing**

Parallel processing is a computational model that enables the simultaneous execution of multiple processes, significantly enhancing performance and efficiency. At its core, the principles of parallel processing hinge on dividing complex problems into smaller, manageable tasks that can be executed concurrently. This strategy reduces

processing time and optimizes resource utilization, making it particularly advantageous in engineering applications where time constraints are critical. The architecture of transputers, designed specifically for parallel processing, embodies these principles, allowing engineers to harness the full potential of concurrent computing.

One of the foundational principles of parallel processing is the concept of task decomposition. This involves breaking down a large problem into discrete tasks that can be executed in parallel. In transputer architectures, each transputer can manage its own processes, facilitating effective task distribution. Engineers must carefully analyze the dependencies between tasks to ensure that they can be executed concurrently without causing bottlenecks. By structuring tasks to maximize independence, the overall performance of a parallel processing system can be significantly enhanced.

Another critical principle is data locality, which emphasizes the importance of minimizing data transfer between processing units. In parallel processing, the efficiency of operations can be dramatically improved when data is kept close to the processing units that require it. Transputers are designed with memory management in mind, allowing each unit to access local memory quickly. This principle is particularly relevant in embedded systems where memory bandwidth is often a limiting factor. By leveraging data locality, engineers can design systems that are not only faster but also more energy-efficient, a crucial consideration in many engineering applications.

Synchronization and coordination between parallel tasks are also essential principles in parallel processing. As multiple processes execute simultaneously, mechanisms must be in place to manage their interactions and ensure that shared resources are accessed in a controlled manner. Transputers provide built-in communication protocols that facilitate effective synchronization. Engineers must implement strategies for managing inter-process communication to avoid issues such as race conditions and deadlocks, thereby ensuring the reliability and correctness of parallel systems.

Finally, scalability is a vital principle in the realm of parallel processing. As problems grow in complexity and size, the ability to scale processing resources effectively becomes paramount. Transputers are inherently designed to support scalability, enabling engineers to expand their systems as needed without significant redesign efforts. This adaptability allows engineering managers to plan for future growth, ensuring that their parallel processing solutions remain viable and efficient in the face of evolving demands. By adhering to these principles, engineers can create robust transputer-based systems that excel in parallel processing, particularly within embedded applications.

## **Types of Parallelism**

Parallelism in computing is a fundamental concept that can be categorized into several types, each serving distinct purposes and applications within the realm of transputer architectures. The most commonly discussed types of parallelism include data parallelism, task parallelism, pipeline parallelism, and fine-grained versus coarse-grained parallelism. Understanding these categories is essential for engineers and engineering managers involved in the design and implementation of parallel processing systems, particularly those utilizing transputers.

Data parallelism focuses on distributing data across multiple processing elements, enabling simultaneous processing of data subsets. This type of parallelism is especially beneficial in applications requiring large-scale data processing, such as image processing or scientific simulations. By breaking down a large

dataset into smaller chunks, engineers can leverage the processing power of multiple transputers to perform computations concurrently, significantly reducing processing time and enhancing performance. This approach is highly efficient for problems that exhibit regular data structures and can be efficiently mapped to transputer architectures.

Task parallelism, in contrast, involves the distribution of different tasks or functions across multiple processing units. Each task can be executed independently, allowing for flexible approach to parallel more а processing. This type of parallelism is particularly advantageous in scenarios where tasks are heterogeneous and require

different algorithms or processing techniques. Engineers can design systems that dynamically allocate transputer resources to various tasks based on current workloads, ensuring optimal use of processing capabilities and improving system responsiveness and efficiency. Pipeline parallelism introduces a different approach by organizing tasks into a sequence of stages, where the output of one stage becomes the input for the next. This technique allows for continuous processing, as different stages can

operate simultaneously on different data elements. In transputer architectures, pipeline parallelism can be effectively implemented to enhance throughput in applications such as digital signal processing or real-time data analysis. Engineers must carefully design the pipeline stages to minimize delays and optimize the flow of data between transputers, ensuring that each stage is adequately balanced to maintain high performance.

| Fine-Grained | Coarse-Grained |

|--------------|----------------|

|              |                |

|              |                |

|              |                |

|              |                |

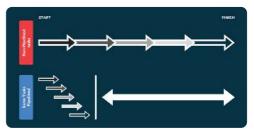

The distinction between fine-grained and coarse-grained parallelism further illustrates the diversity in parallel processing designs. Fine-grained parallelism involves a high degree of task division, where small,

independent tasks are executed in parallel. This approach can lead to significant overhead due to increased communication between processing units. In contrast, coarse-grained parallelism entails larger, more substantial tasks, which can reduce communication overhead but may lead to underutilization of processing resources if not managed carefully. Engineers must evaluate the specific requirements of their applications to determine the most suitable approach to parallelism, balancing the tradeoffs between granularity, performance, and complexity.

In conclusion, understanding the various types of parallelism is crucial for engineers and engineering managers working with transputer architectures. Each type offers unique advantages and challenges, influencing the design and implementation of parallel processing solutions. By effectively leveraging data parallelism, task parallelism, pipeline parallelism, and choosing the appropriate granularity, engineers can optimize their systems for enhanced performance and efficiency in parallel processing tasks.

#### **Benefits and Challenges of Parallel Processing**

Parallel processing offers a range of benefits that are particularly advantageous in the context of transputer architectures. One of the primary advantages is the significant improvement in computational speed and efficiency. By distributing tasks across multiple processors, engineers can tackle complex problems that would be infeasible for a single processor to handle in a reasonable timeframe. This capability is especially beneficial in fields such as embedded systems, where real-time processing and quick response times are critical. With transputers facilitating this parallelism, engineers can enhance system performance while optimizing resource utilization.

Another important benefit of parallel processing with transputers is the scalability it provides. As project demands increase, engineers can easily add more transputers to the system without overhauling the entire architecture. This modularity allows for incremental upgrades and adaptability to changing requirements, making it a cost-effective solution for engineering projects. The flexibility to scale up or down based on project needs is invaluable, enabling engineering teams to manage resources efficiently while maintaining performance.

However, the implementation of parallel processing does come with its challenges. One significant obstacle is the complexity of programming and managing parallel tasks. Engineers must develop algorithms that can effectively divide workloads and ensure that processors communicate efficiently. This can require a steep learning curve, especially for those accustomed to traditional, sequential programming paradigms. The need for careful synchronization between processors to avoid issues such as race conditions further complicates the process, demanding more sophisticated design and testing efforts.

Moreover, the overhead associated with managing multiple processors can also pose a challenge. While parallel processing can accelerate computation, the communication and coordination between transputers can introduce latency, potentially offsetting some of the performance gains. Engineers must balance the workload distribution with the overhead of inter-processor communication, which requires careful consideration in the design phase. This balancing act can be particularly challenging in embedded systems, where resources are often constrained, and efficiency is paramount.

In conclusion, while parallel processing using transputer architectures presents numerous advantages, including increased speed, scalability, and resource optimization, it is not without its difficulties. Engineers and engineering managers must navigate the complexities of programming and inter-processor communication to fully leverage the potential of parallel processing. By understanding both the benefits and challenges, engineering teams can make informed decisions when implementing transputer-based solutions in their projects, ultimately leading to more efficient and effective engineering outcomes.

# **Chapter 3: Transputer Architecture**

## **Core Components of Transputers**

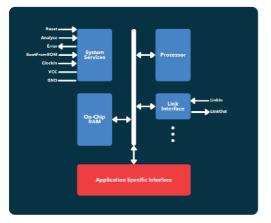

Transputers are specialized microprocessors designed for parallel processing, featuring a unique architecture that optimizes performance for concurrent tasks. At the heart of transputer architecture are several core components that facilitate efficient communication, processing, and scalability. Understanding these components is essential for engineers and engineering managers who are involved in designing systems that leverage transputers for high-performance computing applications.

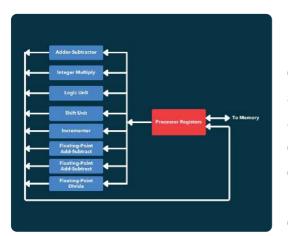

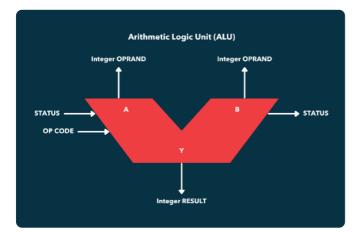

One of the primary components of transputers is the processing unit, which includes the arithmetic logic unit (ALU) and control logic. The ALU performs arithmetic and logical operations, while the control logic manages instruction execution and data

flow within the transputer. This design allows for a high degree of parallelism, enabling multiple operations to occur simultaneously. Consequently, transputers can handle complex computations more efficiently than traditional serial processing architectures.

Another significant component is the memory architecture, which typically employs a combination of local and global memory. Each transputer has its own local memory, allowing for quick access to frequently used data, while global memory is shared among multiple transputers to facilitate interprocessor communication. This hybrid memory model enhances performance by reducing access latency and increasing bandwidth, crucial for applications requiring rapid data exchange among processing units. Communication links represent a vital aspect of transputer architecture, enabling seamless data transfer between processors. Transputers utilize a point-to-point communication model, where each processor can send and receive messages directly to and from its neighbors. This approach minimizes communication overhead and enhances the overall throughput of the system. Engineers can exploit these communication capabilities to design scalable parallel systems that can efficiently distribute workloads across multiple transputers.

Lastly, the operating system and software support are integral to leveraging the full capabilities of transputers. Transputers typically run specialized operating systems that facilitate task scheduling, resource allocation, and inter-process communication. These systems are designed to optimize the use of hardware resources, allowing engineers to focus on application development without being bogged down by low-level hardware management. By understanding these core components, engineers and engineering managers can make informed decisions when implementing transputer-based solutions in their projects.

## **Communication Protocols in Transputers**

Communication protocols in transputers are fundamental to their operation, enabling efficient data exchange in parallel processing environments. Transputers, developed in the 1980s, were designed with integrated communication capabilities that allowed them to connect directly to one another. This architecture facilitates the creation of complex networks of processors, where each transputer can operate independently while still being able to communicate with others. Understanding these protocols is essential for engineers and engineering managers looking to leverage transputer technology in embedded systems and other applications. The primary communication mechanism in transputers is based on message passing. Each transputer has a set of links that allow it to send and receive messages to and from other transputers in the network. This capability is crucial for parallel processing, as it allows for the distribution of tasks across multiple processors without requiring shared memory. By utilizing a standardized message format and communication procedure, transputers can efficiently exchange data, ensuring that operations can be performed concurrently, thus maximizing processing speed and resource utilization.

Transputers support several protocols that dictate how messages are formatted and transmitted. The most commonly used protocol is the FIFO (First In, First Out) queue system, which ensures orderly message handling. Messages sent from one transputer to another are queued and processed in the order they are received, preventing data loss and ensuring synchronization. Engineers must carefully consider these protocols when designing systems to ensure that data integrity and communication efficiency are maintained.

In addition to FIFO, transputers also implement flow control mechanisms to manage the rate of data transmission. This is particularly important in highthroughput scenarios where data congestion can lead to bottlenecks. By employing techniques such as acknowledgment signals and buffering, transputers can adaptively manage communication load, allowing for smooth and continuous data flow across the network. Engineers need to balance between throughput and latency when selecting and configuring these protocols to achieve optimal system performance. The integration of communication protocols in transputers extends their applicability in various fields, including embedded systems. As engineers design applications that require real-time processing and responsiveness, understanding how transputer communication operates becomes even more critical. Effective use of these protocols can lead to improved system reliability and performance, enabling the development of sophisticated solutions in areas such as robotics, telecommunications, and automation. As the industry evolves, mastery of transputer communication protocols will remain a vital skill for engineering professionals.

## **Programming Models for Transputers**

Programming models for transputers are essential for engineers and engineering managers to understand, as they provide the framework for developing efficient parallel processing applications. Transputers are unique in their ability to communicate directly with one another through high-speed links, allowing for the construction of complex systems that can process multiple tasks simultaneously. These programming models leverage the inherent parallelism of transputer architectures, enabling developers to optimize their applications for performance and resource management.

One of the primary programming models utilized with transputers is the messagepassing model. This model relies on the concept of processes communicating through messages rather than shared memory. Each transputer operates as an independent processing unit, capable of sending and

receiving messages to coordinate tasks. This approach simplifies synchronization and helps avoid common pitfalls associated with shared memory, such as race conditions. Engineers can effectively implement distributed applications where each transputer handles a specific task, facilitating modular design and scalability. Another significant model is the dataflow programming model, which emphasizes the flow of data through a network of processing nodes. In this paradigm, the execution of a process is triggered by the availability of input data, allowing for a highly dynamic and responsive system. This model aligns well with the transputer's architecture, enabling engineers to design applications that can adapt to varying data input rates and processing demands. By utilizing dataflow principles, systems can achieve high throughput and low latency, crucial for real-time embedded applications.

Additionally, task parallelism is a key programming model that engineers can exploit when working with transputers. This approach involves breaking down a complex task into smaller, independent subtasks that can be executed simultaneously on multiple transputers. By distributing workloads effectively, engineers can enhance performance and reduce processing time significantly. This model is particularly beneficial in scenarios such as image processing or scientific computations, where large datasets can be processed in parallel, maximizing the efficiency of the transputer network.

Finally, the integration of high-level programming languages into transputer development has further streamlined the programming process. Languages like occam, specifically designed for transputer systems, support concurrent programming constructs that align with the underlying hardware architecture. This integration allows engineers to write code that maps closely to the transputer's capabilities, reducing the complexity of parallel programming. As a result, engineers can focus more on system design and functionality, ensuring that their applications are robust, efficient, and maintainable.

# Chapter 4: Transputers in Parallel Processing

### **Case Studies of Parallel Processing Applications**

parallel processing Case studies of applications highlight the transformative impact of transputer architectures across various engineering domains. One notable case is the application of transputers in real-time signal processing for telecommunications. Engineers designed a usina transputers to manage multiple data streams system simultaneously, allowing for efficient handling of voice and data transmission. The parallel processing capabilities of transputers enabled the system to perform complex algorithms for error correction and signal enhancement, significantly improving the quality and reliability of communication systems. This case illustrates how transputers can enhance performance in time-sensitive applications by distributing tasks across multiple processing units.

Another significant application of transputer architecture can be seen in the automotive industry, specifically in the development of advanced driver-assistance systems (ADAS). Engineers leveraged transputers to create a modular

system that processes data from various sensors, such as cameras, radar, and lidar. The parallel processing features allowed for real-time analysis of the environment, enabling functions like obstacle detection and lanekeeping assistance. This case study underscores the importance of transputers in developing systems that require rapid data processing and decision-making, which are essential for enhancing vehicle safety and functionality. In the realm of robotics, transputers have been instrumental in creating sophisticated control systems for autonomous robots. A case study involving an industrial robot illustrates how transputers were employed to manage multiple control tasks concurrently,

such as motion planning and sensor data integration. The ability to parallelize these tasks allowed for smoother operation and more responsive interaction with the environment. This example demonstrates the effectiveness of transputer architecture in applications where real-time performance and adaptability are critical for success.

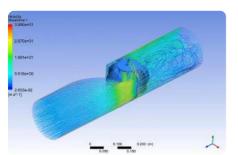

The use of transputers in scientific computing offers another compelling case study, particularly in the field of dynamics computational fluid (CFD). Engineers utilized transputer-based clusters to simulate complex fluid flow scenarios,

significantly reducing computation time compared to traditional serial processing methods. By distributing the computational workload across multiple transputers, researchers were able to tackle larger models and achieve higher resolution simulations. This application highlights the strengths of transputers in handling computationally intensive tasks, allowing engineers to explore more complex phenomena in their simulations.

Lastly, the integration of transputers in embedded systems for medical devices showcases their versatility and reliability. A case study focused on a transputer-based patient monitoring system that processes vital signs from multiple sensors in real-time. The parallel processing capabilities allowed the system to analyze data continuously and provide immediate feedback to healthcare professionals. This application emphasizes the role of transputers in ensuring accurate and timely monitoring in critical care settings, demonstrating their potential for improving patient outcomes through advanced engineering solutions.

#### **Transputers vs. Traditional Processing Architectures**

Transputers represent a significant shift in computing architecture compared to traditional processing systems, primarily due to their inherent parallel processing capabilities. Traditional architectures often rely on a single central processing unit (CPU) to handle multiple tasks sequentially, which can lead to bottlenecks as the complexity of applications increases. In contrast, transputers are designed to operate with multiple processing units that can execute tasks simultaneously, enabling a more efficient handling of computational loads. This parallelism not only accelerates processing times but also enhances the overall system responsiveness, making transputers particularly advantageous in real-time applications.

One of the key differences between transputers and traditional architectures is their communication model. Traditional systems typically utilize a bus architecture where all components share a common communication pathway. This can lead to contention and reduce efficiency as multiple components vie for access. Transputers, however, employ a point-to-point communication model, allowing direct connections between processing units. This architecture minimizes communication delays and enhances throughput, making it well-suited for applications that require rapid data exchange and processing, such as embedded systems in automotive and aerospace engineering.

Moreover, transputers integrate processing and communication capabilities on a single chip, which contrasts sharply with traditional architectures that often separate these functions across multiple chips. This integration reduces physical space, power consumption, and latency associated with inter-chip communication. For engineers designing compact systems, such as those found in robotics and portable devices, the transputer's compact design offers significant advantages. It allows for the creation of more efficient, lightweight systems without sacrificing performance, which is crucial in today's fast-paced technological landscape. Another important aspect to consider is programmability and ease of use. Traditional architectures often require extensive knowledge of low-level programming and hardware specifics to optimize performance. In contrast, transputer systems utilize a higher-level programming model that abstracts many complexities, making it easier for engineers to develop parallel applications. This accessibility allows engineering teams to focus more on design and functionality rather than getting bogged down by intricate hardware details, facilitating quicker iterations and more innovative solutions in parallel processing tasks.

Finally, the scalability of transputer architectures is a notable advantage over traditional processing systems. While adding more processing power to traditional architectures can lead to diminishing returns due to increased complexity and overhead, transputers can be easily scaled by simply adding more processing units. This modularity enables engineers to design systems that can grow with their needs, accommodating more tasks or processing power as required without a complete redesign. As industries increasingly demand flexible and scalable solutions, the transputer architecture stands out as a robust choice for engineers and engineering managers looking to leverage parallel processing in their projects.

## **Performance Metrics for Transputer Systems**

Performance metrics for transputer systems are crucial for evaluating their effectiveness in parallel processing and embedded applications. Engineers and engineering managers must understand these metrics to optimize system design and ensure that the transputer architecture meets specific performance requirements. Key performance indicators include throughput, latency, scalability, and energy efficiency. Each of these metrics plays a vital role in determining how well a transputer system can handle computational tasks and respond to real-time demands.

Throughput is a primary metric that measures the amount of data processed by the transputer system over a given period. This metric is essential for applications requiring high data rates, such as video processing or large-scale simulations. By analyzing throughput, engineers can identify bottlenecks in data flow and optimize communication protocols between transputers. High throughput indicates an efficient system capable of handling multiple parallel tasks, which is particularly beneficial in embedded systems where real-time processing is critical.

Latency, on the other hand, refers to the time taken for a data packet to travel from the source to the destination within the system. In transputer architectures, minimizing latency is crucial, especially for applications that require immediate feedback, such as control systems in robotics or automotive applications. Engineers must consider factors that contribute to latency, including communication overhead and processing delays. By measuring and reducing latency, engineers can enhance the responsiveness of transputer systems, making them more suitable for time-sensitive tasks.

Scalability is another important performance metric, indicating how well a transputer system can accommodate increased workloads or additional processing units. Engineers need to design systems that maintain performance levels as they scale, ensuring that adding more transputers does not lead to diminishing returns. This involves analyzing how the addition of resources affects communication overhead and synchronization among transputers. A scalable architecture allows for the expansion of embedded systems without significant redesign, making it a vital consideration for engineering managers planning future upgrades.

Finally, energy efficiency has become an increasingly important metric as the demand for low-power solutions grows in embedded systems. Transputer systems must balance performance with power consumption, especially in applications where energy resources are limited. By measuring energy usage relative to processing output, engineers can develop strategies to optimize power efficiency without sacrificing performance. This metric is particularly relevant in mobile and IoT applications, where battery life is critical. By focusing on these performance metrics, engineers can effectively evaluate and enhance the capabilities of transputer systems in various applications.

# Chapter 5: Design Considerations for Transputer Systems

### System Architecture Design

System architecture design in the context of transputer architectures represents a critical pillar in the development of efficient parallel processing systems. Transputers, with their unique capabilities, allow for the creation of highly modular and scalable systems. Engineers must carefully consider the architecture to ensure that it meets the demands of both performance and reliability. This involves understanding the interplay between hardware components, communication protocols, and software frameworks. The design process requires a comprehensive approach that addresses these elements in a cohesive manner, enabling optimal functionality in embedded systems and broader parallel processing applications.

A central aspect of system architecture design is the topology of transputer networks. Engineers need to evaluate different configurations, such as ring, mesh, or tree structures, depending on the application requirements. Each topology presents unique advantages and challenges in terms of communication overhead, fault tolerance, and scalability. For instance, a ring topology may offer simpler communication paths but can become a bottleneck as the number of transputers increases. Conversely, a mesh topology allows for greater parallelism but requires more complex routing algorithms. Understanding these trade-offs is essential for engineering managers to guide their teams in selecting the most suitable architecture for specific projects.

#### **Resource Management and Allocation**

Resource management and allocation in parallel processing systems using transputer architectures is a critical aspect that affects the performance and efficiency of engineering applications. Transputers, designed for concurrent computing, can effectively manage resources such as processing power, memory, and communication bandwidth. Effective resource management ensures that tasks are executed optimally, minimizing idle time and maximizing throughput. Engineers must understand how transputers allocate these resources dynamically and how this impacts system performance under varying workloads.

In transputer systems, resource allocation is often implemented through a combination of static and dynamic strategies. Static allocation defines resource distribution at compile time, which can simplify system design but may not adapt well to changing workloads. Conversely, dynamic allocation allows for real-time adjustments based on current system demands, leading to improved efficiency. Engineers must carefully consider the trade-offs between these strategies, especially in embedded systems where resource constraints are prevalent. The ability to dynamically allocate resources can lead to better performance in applications such as real-time data processing and control systems.

Communication between transputers is another vital element of resource management. Transputers utilize a unique communication model that allows them to pass messages directly between each other, minimizing the need for centralized control. This decentralized approach enhances scalability and fault tolerance. Engineers should design communication protocols that optimize bandwidth usage while ensuring low latency. Effective message passing can significantly improve the overall performance of parallel processing tasks, making it essential for engineers to understand the underlying principles of transputer communication. Moreover, the integration of scheduling algorithms plays a crucial role in resource management. Scheduling determines the order and timing of task execution, which directly impacts resource utilization. Engineers should explore various scheduling techniques tailored for transputer architectures, including priority-based, round-robin, and load balancing methods. Each technique has its advantages and applicability depending on the specific requirements of the engineering project. By selecting the appropriate scheduling algorithm, engineers can enhance system responsiveness and ensure that critical tasks receive the necessary resources in a timely manner.

Finally, monitoring and optimizing resource usage is an ongoing process in transputer-based systems. Engineers should implement tools and methodologies for real-time monitoring of resource allocation, allowing for adjustments as needed. Performance metrics such as CPU usage, memory consumption, and communication latency provide valuable insights into system behavior. Through iterative testing and optimization, engineers can refine their systems to achieve optimal performance. By focusing on resource management and allocation, they can ensure that transputer architectures are utilized to their fullest potential, driving advancements in parallel processing and embedded system design.

## Fault Tolerance in Transputer Systems

Fault tolerance in transputer systems is a critical aspect of ensuring reliable and robust performance in parallel processing environments. Transputers, designed for high-performance computing, are inherently parallel in nature, allowing multiple tasks to run simultaneously. However, this parallelism also introduces complexities in error detection and recovery. Engineers must implement strategies to manage faults effectively, ensuring that the system can continue to operate even in the presence of hardware or software failures. One of the primary methods for achieving fault tolerance in transputer systems is through redundancy. This can be implemented at various levels, including hardware duplication, where critical components are replicated to provide backup in case of failure. Software redundancy also plays a significant role, where multiple instances of processes are executed concurrently, allowing the system to compare results and identify discrepancies. By utilizing both hardware and software redundancy, engineers can enhance the reliability of transputer systems, particularly in applications where downtime is unacceptable.

Error detection mechanisms are essential for maintaining fault tolerance in transputer architectures. Techniques such as checksums, parity bits, and watchdog timers can be utilized to monitor system integrity and identify potential faults before they escalate. For instance, checksums can be employed to verify data integrity during communication between transputers, while watchdog timers can reset a transputer if it becomes unresponsive. Implementing these mechanisms allows engineers to proactively address issues, minimizing the impact of faults on overall system performance.

Recovery strategies are equally important in maintaining fault tolerance. When a fault is detected, the system must have predefined protocols in place to manage the situation effectively. This may involve reinitializing faulty components, rerouting tasks to operational transputers, or employing checkpointing to save the state of a computation periodically. By integrating robust recovery strategies, engineers can ensure that transputer systems can resume normal operations quickly, reducing the risk of data loss and improving overall system resilience. In conclusion, fault tolerance is a vital consideration in the design and implementation of transputer systems for parallel processing and embedded applications. Engineers must carefully balance redundancy, error detection, and recovery strategies to create systems capable of withstanding faults while maintaining high performance. As the demand for reliable computing continues to grow, understanding and applying these principles of fault tolerance will be essential for engineers and engineering managers working with transputer architectures.

# **Chapter 6: Transputers in Embedded Systems**

## **Role of Transputers in Embedded Applications**

Transputers, introduced in the 1980s, revolutionized the landscape of embedded systems by enabling high-performance parallel processing capabilities. Their architecture, characterized by a simple and efficient design, integrates processing elements with on-chip communication links. This allows multiple transputers to be connected in a network, facilitating the execution of concurrent tasks and enhancing overall system performance. Engineers and engineering managers have increasingly recognized the advantages of transputers in various embedded applications, particularly in fields demanding real-time data processing and complex computational tasks.

One of the primary roles of transputers in embedded applications is their ability to handle multiple threads of execution simultaneously. This parallel processing capability is particularly advantageous in real-time systems, such as robotics and automotive applications, where timely data processing is critical. By distributing tasks across several transputers, engineers can ensure that each processing unit focuses on a specific function, resulting in faster response times and improved efficiency. The inherent scalability of transputer networks allows for easy adjustments to system performance based on application demands, making them ideal for evolving engineering projects. Another significant aspect is the transputer's simplicity in communication. Each transputer features built-in communication links, enabling direct data exchange between processors without the need for complex bus architectures. This reduces latency and increases throughput, which is essential in embedded systems where timing is crucial. For engineers, this means that design complexity can be minimized while maintaining high performance. The ease of integrating transputers into existing systems makes them a preferred choice for engineers looking to enhance the functionality of current embedded applications without extensive redesign.

Furthermore, transputers support a range of programming models that facilitate the development of parallel applications. The use of specialized programming languages, such as Occam, which is designed for concurrent processing, allows engineers to leverage the full potential of transputer architectures. This flexibility not only simplifies the coding process but also enhances maintainability and readability of the code. Engineering managers can benefit from this by ensuring that their teams can quickly adapt applications to meet new requirements or incorporate innovative features without a significant learning curve.

In conclusion, the role of transputers in embedded applications is multifaceted, providing engineers with powerful tools to tackle complex processing challenges. Their ability to perform parallel processing, coupled with efficient communication capabilities and supportive programming environments, positions transputers as a vital component in modern embedded systems. As industries continue to evolve and demand more from their technology, the application of transputers will likely expand, making them an essential consideration for engineers and engineering managers focused on optimizing performance in their projects.

#### Integration with Other Embedded Components

Integration of transputers with other embedded components is pivotal for enhancing the performance and functionality of parallel processing systems. Transputers, known for their ability to perform concurrent computations, can be seamlessly integrated with various embedded components such as sensors, actuators, and communication modules. This integration enables engineers to develop systems that can handle complex tasks efficiently. By leveraging transputer architecture, engineers can create more responsive and intelligent embedded systems that can process data in real-time, making them suitable for applications in robotics, automotive systems, and industrial automation.

To achieve effective integration, it is essential to consider the communication protocols and interfaces that connect transputers with other components. Transputers typically use a high-speed serial link for interconnecting multiple units, which allows for rapid data exchange and minimizes latency. Engineers must ensure that the embedded components they choose are compatible with these protocols, allowing for seamless communication. Additionally, the design of the overall system should account for the bandwidth requirements and the processing capabilities of each component to avoid bottlenecks in data flow. This careful consideration will lead to a more efficient system that fully utilizes the parallel processing capabilities of transputers.

Moreover, power management becomes a critical aspect when integrating transputers with other embedded components. As many applications demand energy-efficient solutions, engineers must design systems that optimize power consumption without sacrificing performance. Techniques such as dynamic voltage and frequency scaling (DVFS) can be employed to adjust the power based on the workload dynamically. Integrating power management features with transputer architecture not only enhances energy efficiency but also extends the lifespan of embedded systems, making them more sustainable for long-term use in various applications.

The scalability of systems designed with transputers is another advantage when integrating with other embedded components. Transputers can be added or removed from the system as needed, allowing for flexible scaling according to the application's requirements. This modularity enables engineers to tailor the processing power to the specific demands of their projects, whether that involves upgrading existing systems or developing new applications. Such scalability is especially beneficial in rapidly evolving fields like IoT (Internet of Things), where the requirements for processing and connectivity can change frequently.

Finally, the integration process also involves addressing challenges related to debugging and system validation. As the complexity of embedded systems increases, engineers must implement robust testing and debugging strategies to ensure that all components work harmoniously. Tools and methodologies specific to transputer architecture can facilitate this process, providing engineers with the means to monitor and optimize system performance effectively. By prioritizing thorough validation during the integration phase, engineers can mitigate risks and ensure that the final product meets the desired specifications and reliability standards, ultimately leading to successful deployment in the field.

## **Real-Time Processing with Transputers**

**Real-time** with transputers significant processing represents а advancement in the field of parallel processing, particularly suited for applications requiring rapid response times and high throughput. Transputers are designed with a unique architecture that allows them to communicate efficiently with one another, enabling the simultaneous execution of multiple processes. This capability is essential in real-time systems where decisions must be made quickly based on incoming data. The inherent parallelism of transputers makes them an ideal choice for applications in fields such as robotics, telecommunications, and industrial automation, where timing and performance are critical.

The architecture of transputers facilitates the development of systems that can process information in real time by utilizing their built-in communication channels. Each transputer can operate independently while still being part of a larger network, allowing for the distribution of tasks across multiple units. This decentralized approach not only enhances processing efficiency but also improves fault tolerance. In real-world applications, if one transputer fails, others can continue to function, ensuring that the overall system remains operational. This robustness is particularly valuable in embedded systems where reliability is paramount.

Transputers can be configured in various topologies, allowing engineers to tailor the system to specific application needs. For instance, a mesh or ring configuration can be employed to optimize data flow between processors, reducing latency and improving overall system responsiveness. This flexibility in design is crucial for engineers who must consider factors such as resource availability, processing power, and communication overhead when developing real-time applications. By leveraging the transputer architecture, engineers can create systems that not only meet performance requirements but also adapt to changing conditions and workloads.

In the context of embedded systems, transputers enable the integration of real-time processing capabilities into compact devices. This is particularly beneficial in applications such as automotive control systems, where timely processing of sensor data is critical for safety and performance. The ability to execute parallel tasks means that transputers can manage complex algorithms while still adhering to strict timing constraints. As engineers design these systems, they must pay careful attention to the balance between computational load and real-time requirements, ensuring that all parts of the system work harmoniously.

The future of real-time processing with transputers is promising, especially with the ongoing advancements in technology. As engineers continue to explore new applications and refine existing architectures, the potential for transputers to enhance real-time processing capabilities will expand. Innovations in integration techniques, coupled with the growing demand for efficient and responsive systems, position transputers as a vital component in the evolution of embedded and parallel processing systems. The combination of their processing power, flexibility, and robust communication features makes transputers a compelling choice for engineers seeking to implement real-time solutions in their projects.

# **Chapter 7: Programming Transputers**

#### **Overview of Programming Languages for Transputers**

Transputers were revolutionary in the realm of parallel processing, providing a unique architecture that allowed for efficient computation across multiple processing units. This architecture necessitated the development and adaptation of several programming languages specifically designed to harness the full potential of transputer technology. Understanding the various programming languages available for transputers is crucial for engineers and engineering managers, as it enables them to select the most suitable tools for their specific applications, particularly in parallel processing and embedded systems.

One of the primary languages used for programming transputers is Occam, which was designed with the transputer in mind. Occam is a concurrent programming language that employs a minimalist syntax and emphasizes process communication through channels. This language allows engineers to easily express parallelism, making it highly effective for applications that require multiple processes to operate simultaneously. The inherent support for concurrency makes Occam an ideal choice for developing systems that leverage the transputer's capabilities, particularly in the context of real-time data processing and control systems in embedded applications.

Another notable language is C, which has been adapted for use with transputers through the implementation of specialized libraries and extensions. C provides a more familiar environment for many engineers, making it easier to integrate transputer technology into existing projects. Coupled with its efficiency and versatility, C allows for low-level memory management, which is essential for optimizing performance in parallel processing tasks. The ability to write performance-critical code while still managing multiple processing units makes C a widely-used option in the transputer ecosystem, particularly for applications requiring high-speed computation and robust system interactions.

In addition to Occam and C, there are other languages and frameworks that facilitate programming for transputers. For instance, the use of High-Level Synthesis (HLS) tools allows engineers to design and implement transputer-based systems using higher-level constructs. These tools can automatically generate efficient hardware descriptions from high-level programming languages such as C++ or SystemC. This approach not only accelerates the development process but also allows engineers to focus on the algorithmic aspects of their designs rather than getting bogged down in the complexities of low-level programming, thereby enhancing productivity in parallel processing applications.

Finally, as transputer technology continues to evolve, newer languages and paradigms are emerging to support modern engineering challenges. Languages like Python, with its rich ecosystem of libraries for scientific computing and data analysis, are being adapted for use in transputer environments, particularly as the demand for multi-core and distributed computing grows. The integration of these contemporary programming languages with transputer architecture reflects a broader trend towards accessibility and ease of use in parallel processing, enabling engineers to leverage powerful tools without requiring extensive expertise in lower-level programming languages. This adaptability ensures that transputers remain relevant in an ever-changing technological landscape, allowing engineers to implement sophisticated parallel processing solutions across various sectors.

#### **Developing Efficient Parallel Algorithms**

Developing efficient parallel algorithms is crucial for leveraging the full potential of transputer architectures in engineering applications. Transputers, with their built-in capabilities for parallel processing, enable the execution of multiple tasks simultaneously, significantly improving computational speed and efficiency. To create effective parallel algorithms, engineers must consider various factors, including task decomposition, data distribution, and synchronization mechanisms. By addressing these components, engineers can design algorithms that maximize the performance of transputer systems while minimizing overhead and latency.

The first step in developing parallel algorithms is task decomposition, where a complex problem is divided into smaller, manageable sub-tasks that can be executed concurrently. Engineers should analyze the problem to identify independent operations that do not require sequential execution. This decomposition allows for better resource utilization across transputers, as each unit can independently process its assigned sub-task. It is essential to strike a balance between the granularity of tasks; overly fine decomposition can lead to excessive overhead in communication and synchronization, while too coarse a division may not fully exploit the parallel processing capabilities of the architecture.

Data distribution plays a vital role in the performance of parallel algorithms. Engineers need to ensure that data is distributed effectively across the transputer network to minimize communication overhead and maximize locality of reference. Techniques such as data partitioning or replication can be employed to optimize access patterns. In cases where data dependencies exist, thoughtful design can help mitigate bottlenecks caused by contention. Engineers should also consider the memory architecture of transputers, as it can influence how data is accessed and manipulated across different processing units. Synchronization is another critical aspect of developing efficient parallel algorithms. While transputers facilitate concurrent execution, managing access to shared resources is essential to avoid conflicts and ensure data consistency. Engineers must implement appropriate synchronization mechanisms, such as locks, semaphores, or message passing, to coordinate the execution of parallel tasks. Careful design of these mechanisms is necessary to minimize contention and ensure that the performance gains from parallelism are not overshadowed by the overhead introduced by excessive synchronization.

Finally, performance evaluation and optimization are integral to the development process. Engineers should employ profiling tools to identify performance bottlenecks and analyze the efficiency of their parallel algorithms. This evaluation allows for iterative improvements, where algorithms can be fine-tuned based on empirical data. Additionally, engineers should remain aware of the evolving landscape of transputer technologies and parallel processing paradigms, adapting their approaches to leverage new advancements. By focusing on these principles, engineers can develop efficient parallel algorithms that significantly enhance the capabilities of transputer architectures in embedded systems and engineering applications.

#### **Debugging and Optimization Techniques**

Debugging and optimization are critical steps in the development of applications that utilize transputer architectures, particularly due to the inherent complexity of parallel processing. Engineers must understand how to effectively identify and resolve issues that arise when multiple processes execute simultaneously. Debugging in a transputer environment often requires specialized tools and techniques that differ from traditional sequential programming. Engineers need to utilize debuggers specifically designed for parallel systems, which allow for monitoring the state of each transputer and provide insights into message passing and synchronization issues. Understanding the intricacies of these tools is essential for pinpointing deadlocks, race conditions, and other concurrency-related bugs.

To optimize performance in transputer-based systems, engineers must consider both the hardware and software aspects of the architecture. Performance bottlenecks often arise from inefficient communication between transputers or suboptimal resource allocation. Engineers should adopt profiling tools that can analyze the performance of parallel applications, enabling them to identify which transputers are underutilized or overloaded. By collecting runtime metrics, engineers can make informed decisions on how to redistribute workloads across the transputer network, ensuring that all processing units operate at peak efficiency.

Another effective optimization technique involves minimizing intertransputer communication. Engineers should design algorithms that reduce the frequency and volume of messages exchanged between transputers, as excessive communication can lead to increased latency and reduced throughput. Implementing local computations before sending results can significantly decrease the need for data transmission. Furthermore, engineers should leverage techniques such as data locality and partitioning to enhance performance, ensuring that related data is processed in close proximity within the transputer architecture. In addition to these strategies, engineers must also focus on optimizing the memory usage of their applications. Transputers possess limited memory resources, and efficient memory management is crucial for maximizing performance. Techniques such as memory pooling, garbage collection, and careful allocation strategies can help minimize fragmentation and improve access times. Engineers should also consider the trade-offs between computation and memory costs, aiming to balance the two in order to ensure that their applications run efficiently within the constraints of the transputer environment.

Finally, continuous testing and profiling during the development cycle are essential for maintaining optimal performance in parallel processing applications. Engineers should adopt an iterative approach, regularly testing their code against performance benchmarks and real-world scenarios. This ongoing evaluation allows for the identification of new bottlenecks and the implementation of further optimizations as needed. By cultivating a rigorous debugging and optimization process, engineers can enhance the reliability and efficiency of their transputer-based applications, ultimately leading to more robust and scalable solutions in embedded systems and parallel processing environments.

# Chapter 8: Future Trends in Transputer Technology

#### **Emerging Applications and Innovations**

Emerging applications and innovations in transputer architectures are reshaping the landscape of parallel processing. Engineers are increasingly recognizing the advantages of transputer systems in handling complex computational tasks that require high efficiency and scalability. With the rise of big data and the Internet of Things (IoT), transputers have become pivotal in developing systems that can process vast amounts of information in real time. Their ability to communicate rapidly and manage multiple processes simultaneously makes them ideal candidates for applications such as smart grids, autonomous vehicles, and advanced robotics.

One of the most promising areas for transputer innovation is in embedded systems. As the demand for more intelligent and responsive devices grows, engineers are leveraging transputer technology to enhance the capabilities of embedded applications. Transputers allow for modular designs that can be easily adapted to specific tasks, enabling the creation of sophisticated control systems in consumer electronics, medical devices, and industrial automation. This flexibility not only improves performance but also facilitates faster development cycles, allowing engineers to bring products to market more efficiently. Furthermore, the integration of transputer architectures with machine learning algorithms is leading to significant advancements in artificial intelligence applications. By harnessing the parallel processing capabilities of transputers, engineers can train models more effectively and deploy them in environments that require low latency and high reliability. This innovation is particularly critical in sectors such as finance, healthcare, and transportation, where real-time decision-making is essential. As these technologies evolve, they are likely to create new opportunities for engineers to innovate and optimize processes across various industries.

The development of cloud computing and edge computing paradigms also presents new opportunities for transputer architectures. Engineers can utilize transputer systems to create distributed computing environments that enhance the processing power available at the edge of networks. This capability is crucial for applications like real-time analytics and video processing, where data is generated at the source and needs immediate processing to derive actionable insights. As organizations increasingly adopt hybrid cloud strategies, the demand for efficient, scalable solutions based on transputer technology is expected to grow.

Finally, the ongoing research in transputer design is paving the way for even more advanced applications. Innovations in materials science and circuit design are leading to faster, more energy-efficient transputers. These developments will allow engineers to address some of the most pressing challenges in parallel processing, such as heat dissipation and power consumption. As transputer architectures continue to evolve, they promise to unlock new frontiers in computing, enabling engineers to tackle increasingly complex problems with unprecedented efficiency and effectiveness.

#### **Evolution of Transputer Design**

The evolution of transputer design marks a significant milestone in the realm of parallel processing and embedded systems. Originally developed in the 1980s by Inmos, the transputer was envisioned to address the limitations of traditional computing architectures, which struggled to efficiently manage parallel tasks. The architecture combined a microprocessor with built-in communication capabilities, enabling multiple transputers to be interconnected in a network. This innovative design allowed for greater scalability and flexibility in processing, paving the way for the widespread use of parallel processing in engineering applications.

As transputer technology advanced, several key features emerged that enhanced their functionality and efficiency. The introduction of a highspeed serial communication link enabled transputers to communicate at remarkable speeds, facilitating the rapid exchange of data between processors. This capability was crucial for applications requiring real-time processing, such as control systems in embedded environments. Moreover, the architecture's support for multiple memory models allowed engineers to optimize memory usage based on application needs, further improving performance in parallel processing scenarios.

The design of transputers also evolved to incorporate more sophisticated programming models. Early implementations relied heavily on the Occam programming language, which was specifically designed for parallel processing on transputer systems. As the technology matured, developers began to explore other programming paradigms, leading to the integration of languages such as C and C++. This flexibility in programming options made transputers more accessible to a broader range of engineers, fostering innovation and experimentation within the field of parallel processing.

In the context of embedded systems, the evolution of transputer design has been particularly impactful. The ability of transputers to operate in constrained environments while maintaining high processing capabilities has made them ideal for applications in robotics, automotive systems, and telecommunications. Their modular design allows for easy integration into existing systems, enabling engineers to enhance functionality without a complete redesign. This adaptability has driven the adoption of transputers in various industries, where reliability and performance are paramount.

Looking toward the future, the evolution of transputer design continues to inspire advancements in parallel processing architectures. Ongoing research into optimizing interconnectivity and exploring new computational models promises to push the boundaries of what transputers can achieve. As engineers and engineering managers seek to leverage these advancements, understanding the historical context of transputer design will be essential for harnessing its full potential in modern applications. The legacy of transputer architecture remains a cornerstone in the pursuit of efficient, scalable, and powerful processing solutions in an increasingly complex technological landscape.

## The Role of Transputers in AI and Machine Learning

Transputers, first introduced in the 1980s by Inmos, were pioneering microprocessors designed specifically for parallel processing. Their architecture, characterized by a unique ability to communicate directly with other transputers, laid the foundation for distributed computing systems. In the context of artificial intelligence (AI) and machine learning (ML), transputers offer a compelling framework for executing complex algorithms and handling large datasets efficiently. Their inherent capability to perform multiple operations simultaneously aligns perfectly with the computational demands of AI and ML applications, making them a valuable asset for engineers in the field.

In AI and ML, the need for high-performance computing is paramount. Transputers facilitate this by enabling parallel processing, which can significantly accelerate the training of neural networks and other machine learning models. By distributing tasks across multiple transputers, engineers can leverage the collective processing power to handle complex calculations and massive data sets more effectively than traditional singleprocessor systems. This not only reduces training time but also enhances the ability to develop more sophisticated models that can learn from larger volumes of data.

Moreover, the modular nature of transputer architecture allows for scalability in AI applications. Engineers can configure networks of transputers to adapt to the specific requirements of different projects, whether it involves processing real-time data streams or executing resource-intensive simulations. This flexibility proves advantageous in embedded systems where space and power constraints are critical. The ability to create tailored configurations ensures that engineers can implement AI solutions that are both efficient and responsive to the demands of their particular applications.