# Optimizing Response Times in Interrupt Handling

# for Embedded Systems

# Lance Harvie Bsc (Hons)

# **Table Of Contents**

| Chapter 1: Introduction to Real-time Response Time<br>Optimization in Interrupt Handling | 3  |

|------------------------------------------------------------------------------------------|----|

| Understanding the Importance of Response Times in                                        |    |

| Embedded Systems                                                                         | 3  |

| Overview of Interrupt Handling in Embedded Systems                                       | 4  |

| Chapter 2: Basics of Interrupt Handling in Embedded Systems                              | 6  |

| Types of Interrupts in Embedded Systems                                                  | 6  |

| Interrupt Service Routines (ISRs)                                                        | 7  |

| Interrupt Latency and Response Time                                                      | 8  |

| Chapter 3: Challenges in Response Time Optimization                                      | 10 |

| Hardware Constraints in Embedded Systems                                                 | 10 |

| Software Complexity in Interrupt Handling                                                | 11 |

| Real-time Operating Systems (RTOS) Considerations                                        | 12 |

| Chapter 4: Techniques for Optimizing Response Times                                      | 14 |

| Priority-Based Interrupt Handling                                                        | 14 |

| Minimizing Interrupt Latency                                                             | 15 |

| Interrupt Coalescing and Aggregation                                                     | 16 |

| Chapter 5: Case Studies and Examples                                                     | 18 |

| Real-world Examples of Response Time Optimization                                        | 18 |

| Performance Comparison of Different Optimization                                         |    |

| Techniques                                                                               | 20 |

| Chapter 6: Tools and Best Practices for Response Time                                    | 22 |

| Optimization                                                                             | 22 |

| Debugging Tools for Analyzing Response Times                                             | 22 |

| Best Practices for Writing Efficient Interrupt Service Routines                          | 23 |

| Chapter 7: Future Trends in Real-time Response Time<br>Optimization                      | 25 |

| Appendix: Additional Resources for Embedded Engineers -<br>Glossary of Terms - Recommended Reading - References | 31 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Handling                                                                                                        | 29 |

| Recommendations for Optimizing Response Times in Interrupt                                                      |    |

| Summary of Key Findings                                                                                         | 28 |

| Chapter 8: Conclusion and Recommendations                                                                       | 28 |

| Hardware Acceleration for Faster Interrupt Handling                                                             | 26 |

| Machine Learning and AI for Response Time Prediction                                                            | 25 |

# Chapter 1: Introduction to Real-time Response Time Optimization in Interrupt Handling

# Understanding the Importance of Response Times in Embedded Systems

As embedded engineers working in the field of real-time response time optimization in interrupt handling, it is crucial to understand the importance of response times in embedded systems. Response time refers to the time taken by a system to respond to an event or stimulus. In the context of embedded systems, response times play a critical role in determining the system's overall performance and reliability.

One of the key reasons why response times are important in embedded systems is their impact on system performance. In real-time systems, timely responses are essential for meeting critical deadlines and ensuring that tasks are executed within the specified time constraints. Failure to meet these deadlines can result in system malfunctions, data loss, or even system failure. By optimizing response times, embedded engineers can improve the overall performance and reliability of the system.

Another important aspect of response times in embedded systems is their impact on system latency. Latency refers to the delay between the occurrence of an event and the system's response to that event. High latency can lead to delays in data processing, communication, and overall system responsiveness. By reducing response times, embedded engineers can minimize system latency and improve the real-time capabilities of the system. Furthermore, understanding response times is crucial for optimizing interrupt handling in embedded systems. Interrupts are signals that temporarily suspend the normal execution of a program to handle a specific event or request. Efficient interrupt handling is essential for ensuring that critical tasks are executed promptly and that the system can respond to external events in a timely manner. By optimizing response times in interrupt handling, embedded engineers can minimize interrupt latency and improve the system's overall performance.

In conclusion, response times play a crucial role in the performance, reliability, and real-time capabilities of embedded systems. By understanding the importance of response times and optimizing interrupt handling, embedded engineers can improve system performance, reduce latency, and enhance the overall reliability of the system. It is essential for embedded engineers working in the field of real-time response time optimization to prioritize response times in their design and development processes.

#### **Overview of Interrupt Handling in Embedded Systems**

In the world of embedded systems, interrupt handling plays a crucial role in ensuring real-time response times for various applications. Interrupts are signals sent by external devices or internal components of the system to the processor, indicating that a specific event has occurred that requires immediate attention. These events can range from input/output operations to timer expirations, and they must be processed quickly to maintain the system's responsiveness.

Embedded engineers are tasked with designing interrupt handling routines that are efficient and optimized for fast response times. This involves carefully managing the priority levels of interrupts, ensuring that critical tasks are given precedence over less important ones. By prioritizing interrupts in this manner, engineers can minimize latency and ensure that time-critical operations are executed without delay. In addition to managing interrupt priorities, embedded engineers must also consider how to minimize the overhead associated with handling interrupts. This includes reducing the time spent on context switching, saving and restoring processor state, and executing interrupt service routines. By optimizing these aspects of interrupt handling, engineers can improve the overall performance of the system and ensure that it meets the requirements for real-time response times.

Furthermore, engineers must also consider the trade-offs involved in interrupt handling. While it is important to minimize latency and overhead, it is also crucial to maintain system stability and reliability. This requires striking a balance between fast response times and predictable behavior, ensuring that the system can recover from unexpected events and continue to function correctly under varying conditions.

Overall, optimizing response times in interrupt handling for embedded systems requires a combination of careful design, efficient implementation, and thorough testing. By understanding the principles of interrupt handling and applying best practices in real-time response time optimization, embedded engineers can create systems that are both responsive and reliable, meeting the demands of today's increasingly complex and interconnected devices.

# Chapter 2: Basics of Interrupt Handling in Embedded Systems

## **Types of Interrupts in Embedded Systems**

In embedded systems, interrupts play a crucial role in ensuring timely and efficient handling of external events. There are several types of interrupts that can occur, each serving a specific purpose in the overall operation of the system. Understanding the different types of interrupts is essential for embedded engineers who are tasked with optimizing response times in interrupt handling.

One common type of interrupt is the external interrupt, which is triggered by an external event such as a signal from a sensor or a communication device. These interrupts are typically used to alert the microcontroller to important events that require immediate attention. By prioritizing external interrupts and optimizing their handling, embedded engineers can ensure that critical tasks are executed with minimal delay.

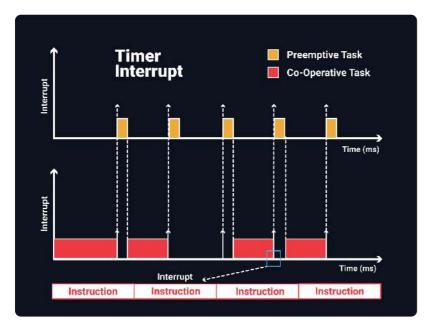

Another of type interrupt is the timer interrupt, which is generated by an internal timer within the microcontroller. Timer interrupts are often used for tasks that require periodic execution, such as updating display screens or monitoring system performance.

By carefully managing timer interrupts and adjusting their frequency, embedded engineers can improve the overall responsiveness of the system. In addition to external and timer interrupts, there are also software interrupts that are triggered by specific instructions in the program code. These interrupts are typically used for tasks that require immediate attention, such as error handling or task prioritization. By optimizing the handling of software interrupts, embedded engineers can ensure that critical tasks are executed in a timely manner without sacrificing system performance.

Overall, understanding the different types of interrupts in embedded systems is essential for optimizing response times in interrupt handling. By prioritizing external interrupts, managing timer interrupts, and optimizing software interrupts, embedded engineers can improve the overall responsiveness of the system and ensure that critical tasks are executed with minimal delay. By implementing efficient interrupt handling strategies, embedded engineers can enhance the performance and reliability of embedded systems in real-time environments.

## **Interrupt Service Routines (ISRs)**

Interrupt Service Routines (ISRs) play a crucial role in the functioning of embedded systems by handling external events or signals in a timely manner. In real-time systems, it is essential to optimize the response times of ISRs to ensure that critical tasks are executed promptly. This subchapter will delve into the importance of ISRs in embedded systems and provide strategies for optimizing response times in interrupt handling.

One key aspect of ISRs is their ability to handle interrupts quickly and efficiently. When an interrupt occurs, the ISR must be able to respond immediately to prevent any delays in processing critical tasks. This requires careful design and implementation of ISRs to minimize latency and maximize throughput. Embedded engineers must be mindful of the hardware constraints and system requirements when designing ISRs to ensure optimal performance. To optimize response times in interrupt handling, it is important to prioritize interrupts based on their criticality. By assigning priorities to interrupts, embedded engineers can ensure that high-priority tasks are processed first, minimizing delays and improving overall system performance. Additionally, utilizing interrupt nesting and preemption techniques can further enhance the responsiveness of ISRs, allowing for faster context switching and execution of multiple tasks concurrently.

Another key consideration in optimizing ISRs is reducing interrupt latency. Interrupt latency refers to the time it takes for the system to respond to an interrupt and begin executing the corresponding ISR. By minimizing interrupt latency, embedded engineers can improve the overall responsiveness of the system and ensure that critical tasks are executed in a timely manner. Techniques such as disabling interrupts during critical sections of code and utilizing hardware features like interrupt controllers can help reduce interrupt latency and improve system performance.

In conclusion, optimizing response times in interrupt handling is essential for embedded engineers working on real-time systems. By prioritizing interrupts, reducing interrupt latency, and implementing efficient ISR design techniques, engineers can ensure that critical tasks are executed promptly and system performance is maximized. With careful planning and attention to detail, embedded engineers can create highly responsive embedded systems that meet the demanding requirements of real-time applications.

## Interrupt Latency and Response Time

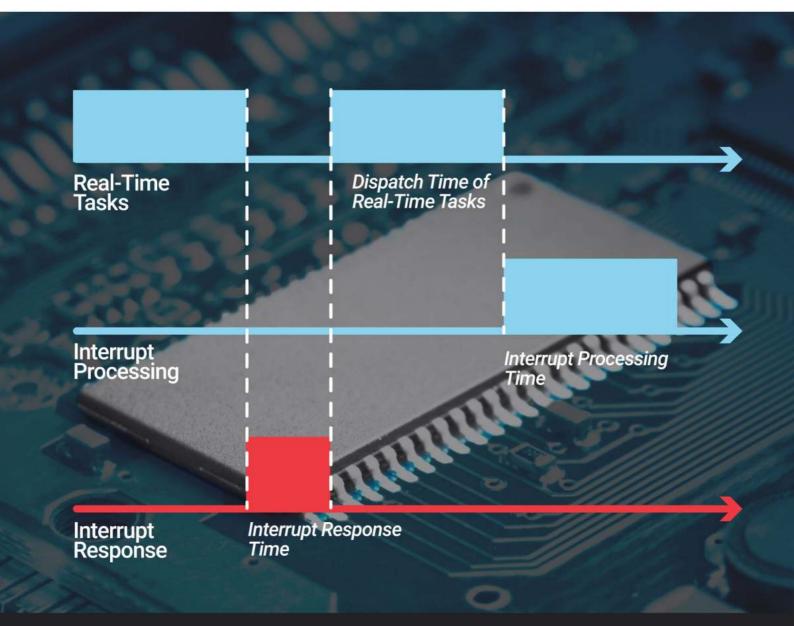

Interrupt latency and response time are critical factors in the performance of embedded systems, especially in real-time applications where timely responses are essential. Interrupt latency refers to the delay between the occurrence of an interrupt and the execution of the corresponding interrupt service routine (ISR). This delay can have a significant impact on the overall response time of the system, as it determines how quickly the system can react to external events. One way to optimize interrupt latency is to minimize the time it takes for the processor to switch from executing the main program to executing the ISR. This can be achieved by reducing the number of instructions that need to be executed before entering the ISR, as well as by minimizing the time it takes to save and restore the processor state. Techniques such as using fast interrupt entry mechanisms and optimizing the ISR code can help reduce interrupt latency and improve the system's responsiveness.

Response time, on the other hand, refers to the time it takes for the system to complete the execution of an interrupt service routine and resume normal operation. This includes not only the execution time of the ISR itself but also any additional processing that may be required before the system can return to its previous state. Optimizing response time involves not only minimizing the latency of the interrupt handling process but also ensuring that the ISR is designed to be as efficient as possible.

One common technique for optimizing response time is to prioritize interrupts based on their importance and criticality to the system. By assigning different priority levels to interrupts and ensuring that highpriority interrupts are serviced quickly, embedded engineers can ensure that the most critical tasks are handled in a timely manner. Additionally, techniques such as interrupt nesting and preemption can help reduce response time by allowing higher-priority interrupts to preempt lowerpriority interrupts.

Overall, optimizing interrupt latency and response time is crucial for ensuring the real-time performance of embedded systems. By understanding the factors that contribute to interrupt latency and response time, and employing techniques to minimize these delays, embedded engineers can design systems that are more responsive and reliable in critical applications.

# Chapter 3: Challenges in Response Time Optimization

### Hardware Constraints in Embedded Systems

As embedded engineers working in the field of real-time response time optimization in interrupt handling, it is crucial to understand the hardware constraints that can impact the performance of embedded systems. Hardware constraints play a significant role in determining the response times of interrupt handling routines, and being aware of these constraints is essential for achieving optimal performance.

One of the primary hardware constraints in embedded systems is the limited processing power of microcontrollers or These microprocessors. finite devices have computational resources, and the complexity of

interrupt handling routines can consume a significant portion of these resources. To optimize response times, engineers must carefully design interrupt handling routines to minimize the use of processing power while still ensuring timely responses to interrupts.

Another hardware constraint that can impact response times is the limited memory available in embedded systems. Memory constraints can restrict the amount of data that can be stored and processed during interrupt handling routines, leading to potential delays in response times. Engineers must carefully manage memory usage and prioritize critical data to ensure efficient interrupt handling and minimal impact on response times. In addition to processing power and memory constraints, embedded engineers must also consider the limitations of input/output (I/O) interfaces in embedded systems. I/O interfaces can introduce latency in interrupt handling routines, impacting the overall response times of the system. Engineers must optimize I/O operations and minimize the time spent communicating with external devices to ensure timely responses to interrupts.

Overall, understanding and addressing hardware constraints is essential for optimizing response times in interrupt handling for embedded systems. By carefully managing processing power, memory usage, and I/O operations, engineers can design efficient interrupt handling routines that meet the real-time requirements of their applications. Through a combination of hardware-aware design strategies and optimization techniques, embedded engineers can achieve optimal performance in their systems and deliver reliable real-time responses to interrupts.

### Software Complexity in Interrupt Handling

Interrupt handling is a critical aspect of embedded systems design, as it directly impacts the real-time response time of the system. As embedded engineers, it is essential to understand the software complexity involved in handling interrupts efficiently to optimize response times. This subchapter will delve into the intricacies of software complexity in interrupt handling and provide insights on how to improve response times in embedded systems.

One of the key challenges in interrupt handling is managing the prioritization of interrupts. In real-time systems, it is crucial to handle higher priority interrupts first to ensure timely response to critical events. This requires careful design and implementation of interrupt service routines to prioritize interrupt handling based on the criticality of the event.

Another aspect of software complexity in interrupt handling is the need for efficient context switching. When an interrupt occurs, the processor must quickly switch from the current task to the interrupt service routine to ensure timely response. This context switching overhead can impact the overall response time of the system, making it essential to optimize context switching mechanisms for faster interrupt handling.

Furthermore, software complexity in interrupt handling also involves handling nested interrupts. In some systems, multiple interrupts can occur simultaneously, leading to nested interrupt scenarios. Managing nested interrupts requires careful design and synchronization mechanisms to ensure proper handling of interrupts without compromising the real-time response time of the system.

In conclusion, understanding the software complexity in interrupt handling is crucial for optimizing response times in embedded systems. By prioritizing interrupts, optimizing context switching mechanisms, and effectively handling nested interrupts, embedded engineers can improve the real-time performance of their systems. With careful design and implementation of interrupt handling routines, it is possible to achieve faster response times and enhance the overall performance of embedded systems.

### **Real-time Operating Systems (RTOS) Considerations**

Real-time Operating Systems (RTOS) are an essential component in embedded systems that require precise timing and quick response times. When considering an RTOS for your embedded system, there are several key factors to keep in mind to optimize response times in interrupt handling. First and foremost, it is crucial to choose an RTOS that is specifically designed for real-time applications. Not all operating systems are created equal, and using a general-purpose operating system may not provide the level of determinism and reliability required for real-time systems. Look for an RTOS that offers features such as priority-based scheduling, deterministic task switching, and minimal interrupt latency.

In addition to selecting the right RTOS, it is important to carefully configure the system to minimize interrupt handling overhead. This includes optimizing interrupt service routines (ISRs) to be as efficient as possible and reducing unnecessary interrupts whenever possible. By minimizing the time spent in interrupt service routines, you can improve overall system responsiveness and reduce the likelihood of missed deadlines.

Another consideration when working with RTOS is the utilization of hardware resources. Make sure to allocate system resources such as CPU time, memory, and peripherals efficiently to avoid bottlenecks and ensure smooth operation of the system. By carefully managing resource usage, you can prevent resource contention and optimize response times in interrupt handling.

Lastly, it is important to thoroughly test and validate the real-time performance of your system before deployment. Use tools such as profiling and tracing to identify potential bottlenecks and areas for improvement. By continuously monitoring and optimizing the system, you can ensure that it meets the required response time specifications and operates reliably in real-world scenarios.

In conclusion, selecting the right RTOS, optimizing interrupt handling overhead, managing hardware resources effectively, and testing system performance are all critical considerations when aiming to optimize response times in interrupt handling for embedded systems. By focusing on these key areas and continuously improving the system, embedded engineers can create highly responsive and reliable real-time systems for a variety of applications.

# Chapter 4: Techniques for Optimizing Response Times

#### **Priority-Based Interrupt Handling**

Priority-based interrupt handling is a critical aspect of optimizing response times in embedded systems. In real-time systems, where timing constraints must be met to ensure proper functioning, the ability to prioritize interrupts based on their importance is essential. By assigning priorities to various interrupts, embedded engineers can ensure that higher priority interrupts are serviced before lower priority ones, minimizing response times and improving overall system performance.

One key benefit of priority-based interrupt handling is the ability to ensure that critical tasks are executed in a timely manner. By assigning higher priorities to interrupts that require immediate attention, such as real-time data processing or sensor input, engineers can guarantee that these tasks are completed without delay. This is especially important in applications where timing is crucial, such as in industrial automation or medical devices.

Another advantage of priority-based interrupt handling is the ability to avoid interrupt conflicts. In systems where multiple interrupts can occur simultaneously, it is important to prioritize them based on their importance. By assigning priorities to interrupts, engineers can resolve conflicts and ensure that critical tasks are not delayed or interrupted by lower priority tasks. This can help improve system stability and reliability, especially in complex embedded systems. In addition to improving response times, priority-based interrupt handling can also help optimize system resource utilization. By prioritizing interrupts based on their importance, engineers can allocate system resources more efficiently, ensuring that critical tasks are given the resources they need to execute quickly and effectively. This can lead to improved system performance and reduced overhead, ultimately resulting in a more efficient and reliable embedded system.

Overall, priority-based interrupt handling is a powerful tool for optimizing response times in embedded systems. By assigning priorities to interrupts based on their importance, engineers can ensure that critical tasks are executed in a timely manner, avoid conflicts, and optimize system resource utilization. This can help improve system performance, stability, and reliability, making it an essential technique for embedded engineers working on real-time response time optimization in interrupt handling.

## **Minimizing Interrupt Latency**

Interrupt latency is a critical factor in the real-time response of embedded systems. By minimizing interrupt latency, embedded engineers can ensure that their systems respond quickly and predictably to external events. This subchapter will explore various techniques and best practices for reducing interrupt latency in order to optimize response times in embedded systems.

One key strategy for minimizing interrupt latency is to prioritize interrupts based on their criticality. By assigning different priority levels to various interrupts, embedded engineers can ensure that the most important interrupts are processed quickly and efficiently. This can help to minimize the overall interrupt latency in the system and improve real-time response times. Another important consideration in minimizing interrupt latency is to carefully manage the interrupt handling process. This includes optimizing interrupt service routines to be as short and efficient as possible, as well as minimizing any unnecessary delays or overhead in the interrupt handling process. By streamlining the interrupt handling process, embedded engineers can reduce interrupt latency and improve overall system performance.

In addition to prioritizing interrupts and optimizing interrupt handling routines, it is also important to carefully analyze the timing characteristics of the system as a whole. By understanding the timing requirements of the various components in the system, embedded engineers can better identify potential sources of interrupt latency and implement targeted optimizations to address them. This holistic approach to minimizing interrupt latency can help to ensure that the system meets its real-time response requirements.

In conclusion, minimizing interrupt latency is a crucial aspect of optimizing response times in embedded systems. By prioritizing interrupts, optimizing interrupt handling routines, and carefully analyzing system timing characteristics, embedded engineers can reduce interrupt latency and improve overall system performance. By following the techniques and best practices outlined in this subchapter, embedded engineers can achieve faster and more predictable real-time response times in their embedded systems.

#### Interrupt Coalescing and Aggregation

Interrupt coalescing and aggregation are techniques used to optimize the response times in interrupt handling for embedded systems. These techniques are crucial for ensuring real-time performance in systems where interrupt handling is critical. By combining multiple interrupts into a single, aggregated interrupt, the system can reduce the overhead associated with handling individual interrupts, thereby improving overall system performance.

Coalescing interrupts involves merging multiple interrupts that occur within a short timeframe into a single interrupt. This reduces the number of interrupt service routines that need to be executed, minimizing the overhead associated with processing interrupts. By coalescing interrupts, the system can prioritize and handle them more efficiently, leading to improved response times and reduced latency.

Aggregating interrupts takes coalescing a step further by combining related interrupts into a single, aggregated interrupt. This technique is particularly useful in systems where multiple interrupts are generated by the same source or event. By aggregating these interrupts, the system can process them as a single entity, reducing the overall processing time and improving system performance.

Interrupt coalescing and aggregation require careful design and implementation to ensure that the system functions correctly and efficiently. Embedded engineers must consider factors such as interrupt priorities, timing constraints, and system resources when implementing these techniques. Properly tuning the interrupt handling mechanisms can significantly improve the real-time response times of the system, making it more reliable and efficient.

In conclusion, interrupt coalescing and aggregation are powerful techniques for optimizing response times in interrupt handling for embedded systems. By combining multiple interrupts into single, aggregated interrupts, the system can reduce overhead, improve efficiency, and enhance overall system performance. Embedded engineers should carefully consider these techniques when designing real-time systems to ensure that interrupt handling is both efficient and reliable.

# **Chapter 5: Case Studies and Examples**

### **Real-world Examples of Response Time Optimization**

In the world of embedded systems, response time optimization is crucial to ensure the smooth and efficient operation of devices. One of the key areas where response time optimization plays a critical role is interrupt handling. Interrupts are signals sent by hardware devices to the CPU to request immediate attention. In real-time systems, minimizing the response time to interrupts is essential to meet timing constraints and maintain system reliability.

To better understand the importance of response time optimization in interrupt handling, let's take a look at some realworld examples. One common example is in automotive systems, where interrupts are

used to handle critical events such as engine faults or braking signals. In these scenarios, a delay in processing interrupts can have serious consequences, leading to potential accidents or system failures. By optimizing response times in interrupt handling, engineers can ensure that these critical events are addressed promptly and efficiently. Another example of response time optimization in interrupt handling can be seen in medical devices. In devices such as pacemakers or insulin pumps, interrupts are used to respond

to changes in patient conditions or deliver life-saving treatments. In these cases, any delay in processing interrupts can have life-threatening implications. By optimizing response times, embedded engineers can ensure that these devices can react quickly and accurately to changing conditions, ultimately saving lives.

In industrial automation systems, response time optimization in interrupt handling is crucial for maintaining production efficiency and ensuring worker safety. In manufacturing environments, interrupts may be used to detect equipment malfunctions or trigger emergency shutdown procedures. By reducing response times to these interrupts, engineers can minimize downtime, prevent costly equipment damage, and protect workers from potential hazards.

Overall, real-world examples of response time optimization in interrupt handling highlight the critical role that this optimization plays in ensuring the reliability and efficiency of embedded systems. By understanding the importance of response time optimization and implementing best practices in interrupt handling, embedded engineers can develop systems that meet strict timing constraints, respond quickly to critical events, and ultimately improve overall system performance.

# Performance Comparison of Different Optimization Techniques

In the world of embedded systems, response time optimization is crucial for ensuring the real-time performance of devices. One key aspect of response time optimization is interrupt handling, which involves the process of responding to external events in a timely manner. Different optimization techniques can be employed to improve the performance of interrupt handling, and in this subchapter, we will compare the effectiveness of these techniques.

One common optimization technique used in interrupt handling is prioritybased scheduling. In this approach, interrupts are assigned priorities based on their importance, with higher priority interrupts being serviced before lower priority ones. This can help ensure that critical interrupts are handled quickly, reducing overall response times. However, priority-based scheduling can also lead to priority inversion issues, where a lower priority interrupt holds up the handling of a higher priority interrupt.

Another optimization technique that is often used in interrupt handling is interrupt coalescing. This involves combining multiple interrupts into a single, larger interrupt in order to reduce the overhead associated with handling individual interrupts. While interrupt coalescing can help improve efficiency and reduce response times, it can also introduce latency issues if not implemented carefully.

A third optimization technique that is commonly employed in interrupt handling is interrupt preemption. This involves the ability to interrupt the handling of one interrupt in order to service a higher priority interrupt. By allowing for preemptive interrupt handling, response times can be further minimized, ensuring that critical events are processed as quickly as possible. However, preemptive interrupt handling can also introduce complexity and potential race conditions. In addition to these techniques, other optimization strategies such as interrupt batching and interrupt masking can also be used to improve the performance of interrupt handling. By carefully evaluating the strengths and weaknesses of each technique, embedded engineers can determine the most effective approach for optimizing response times in interrupt handling for their specific application. By understanding the performance implications of different optimization techniques, engineers can make informed decisions that will ultimately lead to improved real-time performance in embedded systems.

# Chapter 6: Tools and Best Practices for Response Time Optimization

### **Debugging Tools for Analyzing Response Times**

In the world of embedded systems, response times are crucial for ensuring the smooth operation of devices. When it comes to optimizing response times in interrupt handling, one of the key tasks is to analyze and debug any issues that may be causing delays. In this subchapter, we will explore some of the essential debugging tools that embedded engineers can use to analyze response times and identify potential bottlenecks.

One of the most commonly used tools for analyzing response times in interrupt handling is a real-time operating system (RTOS) debugger. RTOS debuggers allow engineers to monitor and analyze the execution of tasks and interrupts in real-time, providing valuable insights into the timing behavior of the system. By using an RTOS debugger, engineers can identify any tasks or interrupts that are causing delays and take steps to optimize their execution.

Another powerful tool for analyzing response times is a logic analyzer. Logic analyzers allow engineers to capture and analyze the signals on the various buses and interfaces in the system, providing a detailed view of the communication between different components. By using a logic analyzer, engineers can identify any timing issues or bottlenecks in the system and take steps to address them.

In addition to RTOS debuggers and logic analyzers, engineers can also use performance monitoring tools to analyze response times in interrupt handling. Performance monitoring tools allow engineers to measure the execution times of tasks and interrupts, providing valuable data on the performance of the system. By using performance monitoring tools, engineers can identify any areas of the system that are experiencing delays and take steps to optimize their performance. Finally, engineers can also use profiling tools to analyze response times in interrupt handling. Profiling tools allow engineers to gather data on the execution times of different functions and code paths, helping them identify any bottlenecks or inefficiencies in the system. By using profiling tools, engineers can pinpoint the root causes of delays in interrupt handling and take steps to address them, ultimately optimizing the response times of the system.

In conclusion, debugging tools play a crucial role in analyzing response times in interrupt handling and identifying potential bottlenecks. By using tools such as RTOS debuggers, logic analyzers, performance monitoring tools, and profiling tools, embedded engineers can gain valuable insights into the timing behavior of their systems and take steps to optimize their performance. By leveraging these tools effectively, engineers can ensure that their embedded systems deliver fast and reliable real-time response times.

#### **Best Practices for Writing Efficient Interrupt Service Routines**

In the world of embedded systems, interrupt service routines (ISRs) play a crucial role in ensuring real-time response times. Efficient ISRs are essential for minimizing latency and ensuring timely handling of critical events. In this subchapter, we will discuss some best practices for writing efficient ISRs that can help embedded engineers optimize response times in interrupt handling.

One important best practice for writing efficient ISRs is to keep them short and simple. Complex ISRs with excessive code can increase latency and impact the overall system performance. By keeping ISRs concise and focused on handling the interrupt quickly, engineers can minimize response times and improve real-time performance. Another key best practice is to prioritize interrupts based on their criticality. By assigning priorities to interrupts, engineers can ensure that high-priority interrupts are handled quickly and efficiently, while lower-priority interrupts are processed in a timely manner without impacting critical tasks. This can help optimize response times and ensure that the system remains responsive to important events.

Additionally, it is important to avoid blocking operations in ISRs. Blocking operations, such as waiting for input/output operations to complete, can introduce delays and impact the responsiveness of the system. Instead, engineers should use non-blocking techniques, such as using flags or queues to communicate between the ISR and the main program, to ensure that the ISR can quickly handle the interrupt and return control to the main program.

Furthermore, engineers should optimize the use of resources in ISRs to minimize overhead and improve efficiency. This includes minimizing the use of memory and CPU resources, as well as avoiding unnecessary operations that can slow down the ISR. By carefully managing resources and optimizing the code in ISRs, engineers can improve response times and ensure that the system can handle interrupts efficiently.

In conclusion, by following these best practices for writing efficient ISRs, embedded engineers can optimize response times in interrupt handling and improve the real-time performance of their systems. By keeping ISRs short and simple, prioritizing interrupts, avoiding blocking operations, and optimizing resource usage, engineers can ensure that their systems can respond quickly and effectively to critical events.

# Chapter 7: Future Trends in Real-time Response Time Optimization

# Machine Learning and AI for Response Time Prediction

Machine Learning and AI have revolutionized the field of response time prediction in embedded systems. By using advanced algorithms and techniques, engineers can now accurately predict response times in interrupt handling, leading to more efficient and optimized systems. In this subchapter, we will explore the role of Machine Learning and AI in response time prediction and how it can benefit embedded engineers working on real-time systems.

One of the key advantages of using Machine Learning and AI for response time prediction is the ability to analyze vast amounts of data and identify patterns that may not be apparent to human engineers. By training algorithms on historical data, systems can learn to predict response times with a high degree of accuracy, leading to more reliable and efficient systems. This can be especially useful in real-time systems where predicting response times is crucial for meeting strict deadlines.

Another benefit of using Machine Learning and AI for response time prediction is the ability to adapt and improve over time. As systems collect more data and learn from past experiences, algorithms can continuously refine their predictions, leading to even more accurate results. This adaptability is essential in dynamic environments where response times may vary based on a variety of factors.

Furthermore, Machine Learning and AI can help embedded engineers optimize response times by identifying bottlenecks and inefficiencies in the system. By analyzing data from various sensors and components, algorithms can pinpoint areas where improvements can be made, leading to faster and more efficient interrupt handling. This level of optimization can be crucial in real-time systems where even small improvements in response times can make a significant impact. In conclusion, Machine Learning and AI have the potential to revolutionize response time prediction in embedded systems, especially in the niche of real-time response time optimization in interrupt handling. By leveraging advanced algorithms and techniques, engineers can accurately predict response times, adapt and improve over time, and optimize systems for maximum efficiency. As technology continues to evolve, the use of Machine Learning and AI in response time prediction will only become more essential for embedded engineers working on real-time systems.

### Hardware Acceleration for Faster Interrupt Handling

Hardware acceleration is a powerful tool that can be utilized to significantly improve the speed and efficiency of interrupt handling in embedded systems. By offloading certain tasks to dedicated hardware components, the overall response time of the system can be greatly reduced, resulting in improved real-time performance. In this subchapter, we will explore the concept of hardware acceleration for faster interrupt handling and discuss some of the key considerations for implementing this technique in embedded systems.

One of the main benefits of hardware acceleration for interrupt handling is the ability to offload repetitive or time-consuming tasks from the main CPU to specialized hardware components. This can help to reduce the overall processing overhead of interrupt handling, allowing the system to respond more quickly to incoming interrupts. By leveraging hardware acceleration, embedded engineers can achieve faster response times and improved real-time performance without the need for significant changes to the software architecture. In order to effectively utilize hardware acceleration for interrupt handling, it is important to carefully analyze the specific requirements of the system and identify potential opportunities for offloading tasks to dedicated hardware components. This may involve redesigning certain aspects of the hardware architecture to better support accelerated interrupt handling, or integrating specialized hardware modules that are specifically designed for this purpose. By taking a systematic approach to hardware acceleration, embedded engineers can maximize the benefits of this technique and achieve optimal real-time performance.

Another important consideration when implementing hardware acceleration for interrupt handling is the potential impact on system reliability and robustness. While hardware acceleration can significantly improve response times, it is essential to ensure that the accelerated components are properly integrated into the overall system architecture and do not introduce any new points of failure. By carefully testing and validating the hardware acceleration implementation, embedded engineers can mitigate the risk of potential issues and ensure that the system remains stable and reliable under all operating conditions.

In conclusion, hardware acceleration is a valuable tool for optimizing response times in interrupt handling for embedded systems. By offloading certain tasks to specialized hardware components, embedded engineers can achieve faster response times and improved real-time performance without compromising system reliability. By carefully analyzing system requirements, identifying opportunities for acceleration, and validating the implementation, embedded engineers can successfully leverage hardware acceleration to enhance the overall performance of their embedded systems.

# Chapter 8: Conclusion and Recommendations

## Summary of Key Findings

In this subchapter, we will summarize the key findings from our study on optimizing response times in interrupt handling for embedded systems. As embedded engineers working in the niche of real-time response time optimization, it is crucial to understand the importance of efficient interrupt handling in ensuring the timely execution of critical tasks in embedded systems.

One of the key findings from our research is the impact of interrupt latency on overall system performance. We found that reducing interrupt latency can significantly improve the response time of critical tasks in embedded systems. By analyzing the interrupt handling process and identifying potential bottlenecks, we were able to propose several techniques for optimizing interrupt response times, such as prioritizing interrupts based on criticality and minimizing interrupt processing overhead.

Another important finding is the importance of proper interrupt handling design in minimizing response time variability. We observed that inconsistent interrupt response times can lead to unpredictable system behavior and may result in missed deadlines for critical tasks. By designing interrupt handlers with deterministic execution paths and minimizing interrupt processing time, we can ensure more predictable and reliable system performance.

Furthermore, our study highlighted the impact of interrupt coalescing on response time optimization. We found that grouping multiple interrupts into a single batch can reduce the overall interrupt processing overhead and improve system performance. By implementing intelligent interrupt coalescing mechanisms, embedded engineers can achieve better response time optimization without compromising system stability. Overall, our research emphasizes the critical role of efficient interrupt handling in optimizing response times for real-time embedded systems. By understanding the key findings and implementing the proposed optimization techniques, embedded engineers can enhance the performance and reliability of their embedded systems, ensuring timely execution of critical tasks and meeting stringent real-time requirements.

# Recommendations for Optimizing Response Times in Interrupt Handling

In order to optimize response times in interrupt handling for embedded systems, there are several key recommendations that embedded engineers should consider. These recommendations are crucial for ensuring real-time response time optimization in interrupt handling, which is essential for the smooth operation of embedded systems.

First and foremost, it is important for embedded engineers to prioritize interrupt handling routines based on their criticality. By categorizing interrupts as either high-priority or low-priority, engineers can allocate resources accordingly and ensure that critical interrupts are processed in a timely manner. This is especially important in real-time systems where delays in interrupt handling can have serious consequences.

Another important recommendation for optimizing response times in interrupt handling is to minimize the use of blocking code within interrupt service routines. Blocking code can lead to delays in processing interrupts and can impact the overall responsiveness of the system. By keeping interrupt service routines short and efficient, engineers can minimize the impact on response times and ensure that interrupts are handled quickly and effectively. Furthermore, embedded engineers should consider implementing interrupt nesting to improve response times in interrupt handling. By allowing interrupts to be nested, engineers can prioritize critical interrupts over noncritical ones and ensure that the most important tasks are handled first. This can help to reduce response times and improve the overall performance of the system.

Additionally, engineers should consider optimizing interrupt handling routines through the use of hardware accelerators and dedicated interrupt controllers. By offloading interrupt handling tasks to specialized hardware components, engineers can reduce the burden on the main processor and improve response times. This can be especially beneficial in systems with high interrupt rates or complex interrupt handling requirements.

Overall, by following these recommendations and prioritizing real-time response time optimization in interrupt handling, embedded engineers can ensure that their systems are able to respond quickly and efficiently to critical events. By minimizing delays in interrupt handling and optimizing the overall performance of the system, engineers can create embedded systems that are reliable, responsive, and efficient.

# Appendix: Additional Resources for Embedded Engineers - Glossary of Terms -Recommended Reading - References

In this subchapter, we will be providing additional resources for embedded engineers looking to optimize response times in interrupt handling for realtime systems. This includes a glossary of terms commonly used in the field, recommended reading materials, and a list of references for further exploration.

1. **Glossary of Terms**: Understanding the terminology used in real-time response time optimization is crucial for embedded engineers. In this section, we will define key terms such as interrupt latency, context switching, priority inversion, and more. By familiarizing yourself with these terms, you will be better equipped to tackle the challenges of optimizing response times in interrupt handling.

**a. Hardware Acceleration**: Utilizing hardware components to speed up specific computational tasks related to interrupt handling.

**b. Interrupt Latency**: The delay between the occurrence of an interrupt and the start of the corresponding interrupt service routine (ISR).

**c.** Interrupt Service Routine (ISR): The function that executes in response to an interrupt.

**d. Priority-Based Interrupt Handling**: Assigning different priorities to interrupts to manage the order in which they are serviced.

**e. Interrupt Coalescing**: Combining multiple interrupts into a single one to reduce overhead.

**f. Interrupt Nesting**: Allowing an interrupt to be interrupted by another higher-priority interrupt.

**g. Preemptive Scheduling**: An operating system feature where the scheduler is allowed to swap out the currently running task in favor of a higher priority task.

**h. Priority-Based Interrupt Handling**: A method where interrupts are prioritized to determine the order of ISR execution when multiple interrupts occur.

**i. Real-Time Operating Systems (RTOS)**: Operating systems designed to handle tasks with strict timing constraints.

**j. Rate Monotonic Scheduling (RMS)**: A priority assignment algorithm used in real-time systems, where the task with the shortest period gets the highest priority.

2. **Recommended Reading**: For embedded engineers looking to deepen their understanding of real-time response time optimization, we have compiled a list of recommended reading materials. These books cover topics such as interrupt handling techniques, scheduling algorithms, and performance analysis tools. Whether you are a beginner or an experienced engineer, these resources will provide valuable insights into optimizing response times in embedded systems.

a. <u>"Embedded Systems Architecture" by Tammy Noergaard</u> - This book provides an in-depth exploration of architectural choices for designing embedded systems, with a focus on efficient interrupt handling strategies.

b. <u>"Making Embedded Systems: Design Patterns for Great Software" by</u> <u>Elecia White</u> - This book offers practical advice and insights into designing robust embedded systems, including optimizing interrupt mechanisms. 3. **References**: In this section, we have included a list of references for further exploration of the topics covered in this book. These references include research papers, technical articles, and online resources that delve into the intricacies of real-time response time optimization. By consulting these references, you can stay up to date with the latest developments in the field and gain new perspectives on interrupt handling techniques.

#### **Research Papers**

a. <u>"Safe and Structured Use of Interrupts in Real-Time and Embedded</u> <u>Software" by John Regehr</u>: This research paper chapter gives best practices for avoiding stack overflow and dealing with interrupt overload in real-time systems.

b. "PIERES: A Playground for Network Interrupt Experiments on Real-Time Embedded Systems in the IoT": This paper presents a system that simulates different network traffic scenarios to analyze the impact of interrupt handling strategies on real-time embedded systems. It's especially relevant for understanding how network interrupts affect system performance in IoT devices.

c. Interrupt Latency Accurate Measurement in Multiprocessing Embedded Systems by Means of a Dedicated Circuit: This study presents a dedicated hardware tool for accurate measurement of interrupt latency, crucial for verifying compliance with real-time requirements in embedded systems.

#### **Technical Articles & Online Resources**

a. <u>"Embedded device driver design: Interrupt handling" on</u> <u>Embedded.com</u>: This article discusses the impact of interrupt handling on the performance of embedded designs and provides insights on managing interrupt latencies effectively.

**b.** <u>"Interrupt Handling and Real-Time Programming" on unrepo.com</u>: This article offers a comprehensive guide on developing robust and responsive systems by efficiently handling interrupts and applying realtime programming principles. c. <u>The Science Behind Embedded C++: Best Practices for High</u> <u>Performance on codewithc.com</u>: This article discusses the best practices for high-performance embedded systems and covers optimizing interrupt handling and other performance aspects.

d. <u>Concurrency and Interrupts in Microcontrollers and Embedded</u> <u>Systems on AllAboutCircuits.com</u>: This technical article discusses how concurrency is managed in embedded systems, particularly how interrupts are utilized to handle multiple processes with examples of configuring peripherals to manage interrupts efficiently.

#### **Community Forums**

**a.** <u>Stack Overflow</u> - This online forum is useful for getting answers to more technical, coding-related queries regarding interrupt routines and optimization strategies.

**b. Reddit communities** such as <u>r/embedded</u> and <u>r/ECE</u>, where industry professionals share their expertise and discuss various challenges including interrupt handling.

**c.** <u>**EEVblog Forum</u></u> - An electronics engineering community that discusses topics ranging from basic electronics to complex embedded system design.</u>**

Overall, this subchapter serves as a valuable resource for embedded engineers interested in optimizing response times in interrupt handling for real-time systems. By familiarizing yourself with the glossary of terms, exploring the recommended reading materials, and delving into the references provided, you can enhance your expertise in this critical area of embedded systems development. Whether you are a seasoned professional or a newcomer to the field, these resources will help you navigate the complexities of real-time response time optimization and improve the performance of your embedded systems.

# **About The Author**

Lance Harvie Bsc (Hons), with a rich background in both engineering and technical recruitment, bridges the unique gap between deep technical expertise and talent acquisition. Educated in Microelectronics and Information Processing at the University of Brighton, UK, he transitioned from an embedded engineer to an influential figure in technical recruitment, founding and leading

firms globally. Harvie's extensive international experience and leadership roles, from CEO to COO, underscore his versatile capabilities in shaping the tech recruitment landscape. Beyond his business achievements, Harvie enriches the embedded systems community through insightful articles, sharing his profound knowledge and promoting industry growth. His dual focus on technical mastery and recruitment innovation marks him as a distinguished professional in his field.

RunTime Recruitment 2024