# Optimizing Interrupt Latency in Real-Time Operating Systems

A Guide for Embedded Engineers

Lance Harvie Bsc (Hons)

# **Table Of Contents**

| Chapter 1: Introduction to Real-Time Operating Systems      | 2  |

|-------------------------------------------------------------|----|

| What are Real-Time Operating Systems?                       | 2  |

| Importance of Interrupt Latency in RTOS's                   | 3  |

| Chapter 2: Understanding Interrupt Latency                  | 5  |

| Definition of Interrupt Latency                             | 5  |

| Factors affecting Interrupt Latency in RTOS's               | 6  |

| Chapter 3: Interrupt Latency Reduction Strategies in RTOS's | 8  |

| Minimizing Task Preemption Time                             | 8  |

| Utilizing Priority Levels Efficiently                       | 9  |

| Implementing Fast Interrupt Handlers                        | 10 |

| Chapter 4: Interrupt Synchronization Mechanisms in RTOS's   | 12 |

| Semaphore and Mutex Usage                                   | 12 |

| Event Flags and Message Queues                              | 14 |

| Spinlocks and Critical Sections                             | 15 |

| Chapter 5: Case Studies and Practical Examples              | 18 |

| Analysis of Interrupt Latency in a Real-Time System         | 18 |

| Implementing Interrupt Latency Reduction Strategies         | 19 |

| Testing and Validating Interrupt Synchronization Mechanisms | 21 |

| Chapter 6: Conclusion and Future Trends                     | 23 |

| Summary of Key Points                                       | 23 |

| Emerging Technologies in Interrupt Latency Optimization     | 24 |

| Final Thoughts for Embedded Engineers                       | 25 |

| Appendix A: Glossary of Terms                               | 27 |

| Appendix B: Additional Resources for Further Reading        | 28 |

## Chapter 1: Introduction to Real-Time Operating Systems

#### What are Real-Time Operating Systems?

Real-time operating systems (RTOS) are specialized operating systems designed to handle real-time applications that require precise timing and prompt response to events. These operating systems are commonly used in embedded systems, where timing constraints are critical for the proper functioning of the system. Real-time operating systems are distinguished from general-purpose operating systems by their ability to guarantee a certain level of predictability in terms of task execution, interrupt handling, and response time.

One of the key features of real-time operating systems is their ability to prioritize tasks based on their importance and time-criticality. This allows the system to ensure that high-priority tasks are executed in a timely manner, even in the presence of lower-priority tasks. This prioritization mechanism is crucial for meeting the timing constraints of real-time applications, such as those found in automotive, aerospace, and industrial control systems.

Interrupt latency reduction strategies are essential for optimizing the performance of real-time operating systems. Interrupt latency refers to the time it takes for the system to respond to an external event or interrupt. High interrupt latency can lead to missed deadlines and degraded system performance. To reduce interrupt latency, developers can implement techniques such as minimizing interrupt handling time, using hardware acceleration for critical tasks, and optimizing interrupt service routines.

In addition to interrupt latency reduction strategies, real-time operating systems also employ interrupt synchronization mechanisms to coordinate the execution of tasks and ensure timely response to events. Interrupt synchronization mechanisms help prevent race conditions and ensure that critical sections of code are executed without interference from other tasks or interrupts. Common synchronization mechanisms used in real-time operating systems include semaphores, mutexes, and event flags.

Overall, real-time operating systems play a crucial role in ensuring the proper functioning of embedded systems that require precise timing and reliable performance. By implementing interrupt latency reduction strategies and utilizing interrupt synchronization mechanisms, embedded engineers can optimize the performance of real-time operating systems and meet the stringent timing constraints of their applications.

#### Importance of Interrupt Latency in RTOS's

Interrupt latency is a critical factor in real-time operating systems (RTOS's) that must be carefully managed by embedded engineers. The importance of interrupt latency cannot be overstated, as it directly impacts the responsiveness and predictability of a system. In the context of RTOS's, interrupt latency refers to the time it takes for a system to respond to an external event or interrupt. Minimizing interrupt latency is crucial for meeting the stringent timing requirements of real-time applications.

One of the key reasons why interrupt latency is so important in RTOS's is that it directly affects the responsiveness of the system. In real-time applications, such as those found in industries like automotive, aerospace, and medical devices, timely responses to external events are essential. High interrupt latency can lead to missed deadlines, data corruption, and even system failures. By reducing interrupt latency, embedded engineers can ensure that their systems respond quickly and predictably to external events. Interrupt latency reduction strategies in RTOS's play a crucial role in optimizing system performance. These strategies may include minimizing the time spent in interrupt service routines, prioritizing interrupts, and implementing efficient interrupt handling mechanisms. By carefully analyzing and optimizing the interrupt latency in their systems, embedded engineers can improve the overall responsiveness and reliability of their real-time applications.

In addition to reducing interrupt latency, it is also important for embedded engineers to consider interrupt synchronization mechanisms in RTOS's. Interrupt synchronization involves coordinating the execution of multiple interrupts to prevent conflicts and ensure the proper functioning of the system. By implementing effective interrupt synchronization mechanisms, engineers can prevent race conditions, resource contention, and other issues that can arise from concurrent interrupt handling.

In conclusion, interrupt latency is a crucial aspect of real-time operating systems that must be carefully managed by embedded engineers. By minimizing interrupt latency and implementing effective interrupt synchronization mechanisms, engineers can ensure that their systems respond quickly and predictably to external events. By optimizing interrupt latency in RTOS's, embedded engineers can improve the overall performance and reliability of their real-time applications.

### **Chapter 2: Understanding Interrupt Latency**

**Definition of Interrupt Latency**

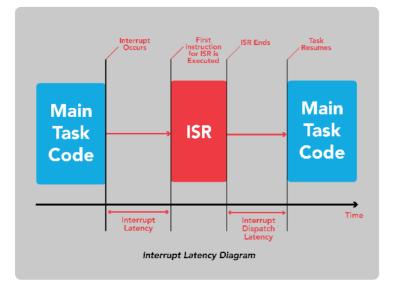

Interrupt latency is а crucial concept in real-time operating systems (RTOS) that plays a significant role determining in the system's responsiveness and overall performance. In simple terms, interrupt latency refers to the time it takes for a system to respond to an external event or interrupt request.

This delay is often measured from the time an interrupt request is generated to the time the system begins executing the corresponding interrupt service routine (ISR).

Reducing interrupt latency is a common goal for embedded engineers working with RTOS's, as it can have a direct impact on the system's ability to meet real-time constraints and deadlines. By minimizing interrupt latency, engineers can ensure that critical tasks are executed in a timely manner, improving overall system reliability and responsiveness. This is particularly important in applications where timing is critical, such as in aerospace, automotive, and industrial control systems.

There are several strategies that can be employed to reduce interrupt latency in RTOS's, including optimizing interrupt handling routines, minimizing interrupt disable times, and prioritizing interrupts based on their criticality. By carefully tuning these parameters and employing best practices, engineers can achieve significant reductions in interrupt latency, leading to improved system performance and reliability. In addition to optimizing interrupt latency, it is also important to consider interrupt synchronization mechanisms in RTOS's. These mechanisms help ensure that interrupts are handled in a coordinated and deterministic manner, preventing conflicts and ensuring that critical tasks are executed in the correct order. By implementing effective interrupt synchronization mechanisms, engineers can further improve system reliability and predictability, leading to more robust and efficient real-time systems.

In conclusion, understanding and optimizing interrupt latency is essential for embedded engineers working with RTOS's. By reducing interrupt latency and implementing effective interrupt synchronization mechanisms, engineers can improve system performance, reliability, and responsiveness, ultimately leading to more successful and efficient realtime embedded systems.

#### **Factors affecting Interrupt Latency in RTOS's**

Interrupt latency in real-time operating systems (RTOS) is a critical factor that can significantly impact the performance and responsiveness of embedded systems. In this subchapter, we will explore the various factors that can affect interrupt latency in RTOS's and discuss strategies for optimizing interrupt latency to meet real-time requirements.

One of the key factors affecting interrupt latency in RTOS's is the priority of the interrupt service routine (ISR). When an interrupt occurs, the RTOS must quickly switch to the ISR and execute it in a timely manner. If the ISR has a low priority, it may be preempted by higher-priority tasks, causing delays in processing the interrupt. To minimize interrupt latency, it is important to assign high priorities to critical ISRs and ensure that they are executed without delay.

Another factor that can impact interrupt latency is the interrupt nesting depth in the RTOS. When multiple interrupts occur simultaneously or in quick succession, the RTOS must handle them in a nested manner, which can introduce additional overhead and increase interrupt latency. By carefully managing interrupt nesting depth and optimizing the handling of nested interrupts, it is possible to reduce interrupt latency and improve system responsiveness.

Interrupt synchronization mechanisms in RTOS's, such as interrupt masking and prioritization, can also play a crucial role in minimizing interrupt latency. By temporarily disabling interrupts during critical sections of code or giving higher priority to time-critical interrupts, it is possible to ensure that important tasks are executed without delay. Additionally, using efficient interrupt handling techniques, such as deferred processing or interrupt chaining, can help reduce interrupt latency and improve system performance.

In conclusion, reducing interrupt latency in RTOS's is essential for meeting real-time requirements in embedded systems. By considering factors such as ISR priority, interrupt nesting depth, and synchronization mechanisms, embedded engineers can optimize interrupt latency and improve system responsiveness. By implementing interrupt latency reduction strategies and leveraging interrupt synchronization mechanisms, it is possible to design reliable and efficient embedded systems that meet the stringent timing constraints of real-time applications.

# Chapter 3: Interrupt Latency Reduction Strategies in RTOS's

#### Minimizing Task Preemption Time

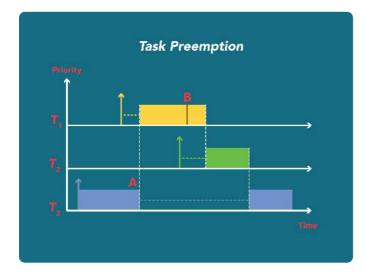

In real-time operating systems (RTOS), minimizing task preemption time is crucial for ensuring efficient and predictable system performance. Task preemption time refers to the duration between when an interrupt occurs and when the RTOS switches from executing a currently running task to handling the interrupt. This delay can impact the responsiveness and determinism of the system, making it essential for embedded engineers to develop strategies to reduce task preemption time.

effective strategy for One minimizing task preemption time is to prioritize interrupts based on their criticality and categorizing urgency. By interrupts into different levels of importance, embedded engineers can assign appropriate priorities to ensure that high-priority interrupts are handled quickly and efficiently.

This can help reduce the overall task preemption time and improve the system's responsiveness to critical events.

Another approach to reducing task preemption time is to implement interrupt synchronization mechanisms within the RTOS. These mechanisms help coordinate the handling of multiple interrupts to minimize conflicts and prevent unnecessary delays. By carefully managing the order in which interrupts are processed, embedded engineers can optimize the use of system resources and reduce the overall task preemption time. Furthermore, embedded engineers can also explore the use of interrupt nesting techniques to minimize task preemption time. Interrupt nesting allows for the handling of multiple interrupts in a hierarchical manner, ensuring that higher-priority interrupts are processed first while lowerpriority interrupts are queued for later execution. This approach can help streamline the interrupt handling process and reduce unnecessary delays, ultimately improving the system's responsiveness and determinism.

Overall, minimizing task preemption time is a critical aspect of optimizing interrupt latency in RTOS's. By implementing effective strategies such as prioritizing interrupts, using interrupt synchronization mechanisms, and exploring interrupt nesting techniques, embedded engineers can enhance the performance and predictability of real-time systems. By understanding the importance of task preemption time and employing appropriate techniques, engineers can develop robust and efficient embedded systems that meet the stringent requirements of real-time applications.

#### **Utilizing Priority Levels Efficiently**

In the world of embedded systems, real-time operating systems (RTOS) play a crucial role in ensuring that tasks are executed in a timely manner. One of the key challenges faced by embedded engineers working with RTOS is managing interrupt latency. Interrupt latency refers to the time it takes for the system to respond to an external event or signal. In order to optimize interrupt latency in RTOS, it is essential to utilize priority levels efficiently.

One strategy for reducing interrupt latency in RTOS is to carefully assign priority levels to different tasks and interrupts. By assigning higher priority levels to time-critical tasks and interrupts, engineers can ensure that these events are processed quickly and without delay. Lower priority tasks can be scheduled to run only when higher priority tasks are not active, minimizing the impact on interrupt latency. In addition to assigning priority levels, engineers can also utilize interrupt synchronization mechanisms in RTOS to further reduce interrupt latency. Interrupt synchronization mechanisms help to manage the order in which interrupts are processed, ensuring that critical events are handled in a timely and efficient manner. By carefully designing interrupt synchronization mechanisms, engineers can minimize the risk of priority inversion and other issues that can cause delays in interrupt processing.

Another important aspect of utilizing priority levels efficiently is to consider the impact of interrupt latency on overall system performance. By carefully analyzing the timing requirements of different tasks and interrupts, engineers can make informed decisions about how to assign priority levels and optimize interrupt processing. This can help to ensure that the system meets its real-time requirements while also maximizing efficiency and performance.

In conclusion, optimizing interrupt latency in RTOS requires a combination of strategies, including assigning priority levels, utilizing interrupt synchronization mechanisms, and carefully analyzing system requirements. By leveraging these techniques, embedded engineers can reduce interrupt latency, improve system responsiveness, and ensure that critical tasks are executed in a timely manner. With a focus on efficient priority level utilization, engineers can effectively manage interrupt latency and enhance the performance of real-time operating systems in embedded systems.

#### **Implementing Fast Interrupt Handlers**

Implementing fast interrupt handlers is crucial for reducing interrupt latency in real-time operating systems (RTOS). Interrupt latency refers to the time it takes for an interrupt to be processed by the system, which can impact the overall responsiveness and performance of the embedded system. In this subchapter, we will discuss strategies for implementing fast interrupt handlers to minimize interrupt latency and improve the real-time responsiveness of the system. One key strategy for implementing fast interrupt handlers is to minimize the amount of processing done within the interrupt handler itself. This can be achieved by offloading time-consuming tasks to lower priority threads or deferred processing mechanisms. By keeping the interrupt handler code concise and efficient, the overall interrupt latency can be reduced, leading to improved system performance.

Another important consideration when implementing fast interrupt handlers is to prioritize and optimize critical sections of code within the handler. By identifying and prioritizing the most time-sensitive tasks, engineers can ensure that these tasks are executed quickly and efficiently, reducing overall interrupt latency in the system.

In addition to optimizing the code within the interrupt handler, engineers should also consider implementing interrupt synchronization mechanisms in the RTOS. These mechanisms help to prevent conflicts and ensure that interrupts are processed in a timely and orderly manner. By using techniques such as disabling interrupts, semaphore signaling, and interrupt masking, engineers can manage interrupt synchronization effectively and further reduce interrupt latency in the system.

Overall, implementing fast interrupt handlers is a critical aspect of reducing interrupt latency in real-time operating systems. By minimizing processing within the handler, prioritizing critical tasks, and implementing interrupt synchronization mechanisms, engineers can improve the real-time responsiveness and performance of embedded systems. By following these strategies, embedded engineers can optimize interrupt latency and enhance the overall reliability and efficiency of their real-time operating systems.

# Chapter 4: Interrupt Synchronization Mechanisms in RTOS's

#### **Semaphore and Mutex Usage**

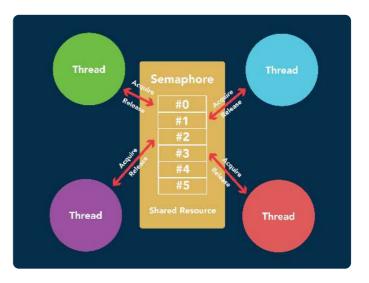

In real-time operating systems (RTOS), managing interrupt latency is crucial for ensuring the system responds to events in a timely manner. One of the key strategies for reducing interrupt latency is the proper use of synchronization mechanisms such as semaphores and mutexes. These mechanisms help ensure that critical sections of code are protected from concurrent access, preventing race conditions and ensuring data integrity.

Semaphores are а synchronization mechanism that allows tasks to signal each other when a resource is available. By usina semaphores, tasks can safely shared access resources without interfering with each other. In the context of interrupt latency reduction, semaphores can be used to

protect critical sections of code that must be executed atomically. By properly implementing semaphores, embedded engineers can ensure that interrupt handlers and tasks do not interfere with each other, reducing overall interrupt latency.

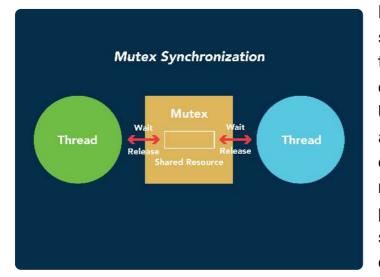

Mutexes another are synchronization mechanism that can be used to protect critical sections of code. Unlike semaphores, mutexes are used to ensure that only one task can access а resource at a time. This is particularly useful in scenarios where tasks need exclusive access to а

resource, such as a shared data structure. By using mutexes, embedded engineers can prevent tasks from accessing critical sections of code concurrently, reducing the likelihood of race conditions and improving system stability.

When implementing semaphores and mutexes in an RTOS, it is important to consider the priority inversion problem. This occurs when a high-priority task is blocked by a lower-priority task that holds a semaphore or mutex. To mitigate this issue, engineers can use priority inheritance or priority ceiling protocols to ensure that tasks are executed in the correct order based on their priority levels. By carefully managing the use of synchronization mechanisms, engineers can reduce interrupt latency and improve the overall performance of their real-time systems.

In conclusion, the proper use of semaphores and mutexes is essential for reducing interrupt latency in real-time operating systems. By carefully implementing these synchronization mechanisms and considering the potential pitfalls such as priority inversion, embedded engineers can ensure that their systems respond to events in a timely and efficient manner. By following best practices and leveraging the capabilities of RTOS, engineers can optimize interrupt latency and improve the overall performance of their embedded systems.

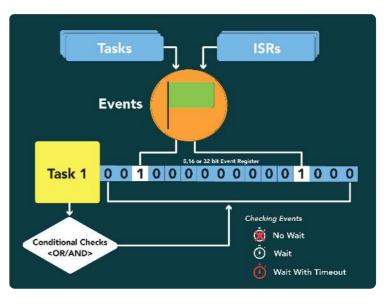

#### **Event Flags and Message Queues**

Event Flags and Message Queues are two important mechanisms in realtime operating systems that can help embedded engineers reduce interrupt latency and improve system performance. In this subchapter, we will discuss how these mechanisms work and how they can be utilized to optimize interrupt handling in RTOS environments.

Event Flags are used to signal the occurrence of a specific event or condition in the system. By setting and clearing these flags, tasks can communicate with each other and synchronize their actions. In the context of interrupt handling, event flags can be used to notify tasks about the completion of

an interrupt service routine, allowing them to take appropriate actions in response.

Message Queues, on the other hand, provide a way for tasks to exchange data and messages in a synchronized and efficient manner. By using message queues, tasks can communicate with each other without the need for direct coupling, reducing the risk of priority inversion and improving overall system performance. In the context of interrupt handling, message queues can be used to pass data from an interrupt service routine to a task for further processing. When it comes to reducing interrupt latency in RTOS environments, event flags and message queues can play a crucial role. By using event flags to signal the occurrence of interrupts and message queues to pass data between tasks, engineers can minimize the time it takes to respond to critical events and improve overall system responsiveness. Additionally, these mechanisms can help synchronize interrupt handling across multiple tasks, ensuring that interrupts are processed in a timely and efficient manner.

In conclusion, event flags and message queues are valuable tools for embedded engineers looking to optimize interrupt latency in real-time operating systems. By leveraging these mechanisms effectively, engineers can improve system performance, reduce latency, and ensure that critical events are handled in a timely and efficient manner. By understanding how these mechanisms work and how they can be applied in RTOS environments, engineers can take their interrupt synchronization strategies to the next level and create more responsive and reliable embedded systems.

#### **Spinlocks and Critical Sections**

Spinlocks and critical sections are essential concepts in real-time operating systems (RTOS) for managing concurrent access to shared resources and minimizing interrupt latency. A spinlock is a synchronization mechanism that allows only one task to access a critical section of code at a time, preventing conflicts and ensuring data consistency. Critical sections are portions of code that must be executed atomically to avoid race conditions and ensure proper operation of the system.

In the context of interrupt latency reduction strategies in RTOS's, spinlocks play a crucial role in ensuring that critical sections are executed efficiently and without delays. By using spinlocks to protect shared resources, embedded engineers can prevent interrupts from accessing critical sections while they are being modified, reducing the risk of data corruption and improving overall system performance. Additionally, spinlocks can help prioritize tasks and ensure that higher-priority interrupts are processed first, minimizing latency and improving real-time responsiveness.

Interrupt synchronization mechanisms in RTOS's rely on spinlocks to coordinate the execution of critical sections and ensure that shared resources are accessed in a controlled and predictable manner. By properly implementing spinlocks and critical sections in their code, embedded engineers can reduce the risk of race conditions and improve the reliability of their real-time systems. This is particularly important in safety-critical applications where timing constraints must be met to prevent catastrophic failures.

To optimize interrupt latency in real-time operating systems, embedded engineers should carefully analyze their code and identify critical sections that could benefit from the use of spinlocks. By implementing spinlocks effectively, engineers can reduce the risk of contention and improve the efficiency of their system's resource management. Additionally, by understanding the nuances of spinlocks and critical sections, engineers can fine-tune their interrupt synchronization mechanisms and achieve lower latency in their real-time applications. In conclusion, spinlocks and critical sections are essential tools for embedded engineers looking to optimize interrupt latency in real-time operating systems. By understanding the role of spinlocks in managing concurrent access to shared resources and implementing critical sections effectively, engineers can improve the performance and reliability of their real-time systems. By following best practices and leveraging spinlocks to synchronize interrupts and protect critical sections, engineers can minimize latency and ensure the timely execution of tasks in their applications.

## Chapter 5: Case Studies and Practical Examples

#### Analysis of Interrupt Latency in a Real-Time System

In real-time systems, interrupt latency is a critical factor that can significantly impact the system's performance and reliability. Interrupt latency refers to the time it takes for the system to respond to an external event or signal by servicing the corresponding interrupt. Minimizing interrupt latency is crucial for real-time systems as it directly affects the system's ability to meet timing constraints and respond to time-sensitive events.

One of the key challenges in optimizing interrupt latency is the complexity of modern real-time operating systems (RTOSs). These operating systems are designed to provide multitasking capabilities, which can introduce additional overhead and delays in handling interrupts. Embedded engineers need to carefully analyze the interrupt latency characteristics of their chosen RTOS and implement strategies to minimize latency while maintaining system stability and reliability.

One effective strategy for reducing interrupt latency in RTOSs is to prioritize and optimize interrupt handling routines. By assigning higher priority levels to time-critical interrupts and streamlining interrupt service routines, engineers can ensure that critical events are processed quickly and efficiently. Additionally, engineers can utilize techniques such as interrupt nesting and preemption to minimize the impact of lower-priority interrupts on the system's response time. Another important aspect of interrupt latency analysis is understanding the synchronization mechanisms employed by the RTOS. Synchronization mechanisms such as semaphores, mutexes, and message queues play a crucial role in coordinating interrupt handling routines and preventing race conditions. Engineers should carefully evaluate the performance of these synchronization mechanisms and optimize their usage to minimize interrupt latency and improve system responsiveness.

Overall, effective analysis of interrupt latency in a real-time system requires a deep understanding of the RTOS's internal workings and the ability to identify and address potential sources of latency. By implementing interrupt latency reduction strategies and optimizing synchronization mechanisms, embedded engineers can improve the realtime performance and reliability of their systems, ensuring that critical events are processed in a timely manner and meeting the stringent timing requirements of their applications.

#### **Implementing Interrupt Latency Reduction Strategies**

As embedded engineers, it is crucial to understand the importance of implementing interrupt latency reduction strategies in real-time operating systems (RTOS). Interrupt latency refers to the time it takes for an interrupt to be recognized and serviced by the system. High interrupt latency can lead to missed deadlines, decreased system responsiveness, and even system failure in time-critical applications. In this subchapter, we will discuss various techniques and best practices for reducing interrupt latency in RTOS environments.

One of the key strategies for reducing interrupt latency is to prioritize critical interrupts over non-critical ones. By assigning different priority levels to interrupts, the RTOS can ensure that time-sensitive tasks are serviced first, minimizing the overall latency in the system. This can be achieved by configuring interrupt controllers and setting up interrupt handling routines to prioritize critical interrupts.

Another effective strategy for reducing interrupt latency is to minimize the time spent in interrupt service routines (ISRs). ISRs should be kept as short and efficient as possible to reduce the overall latency in the system. This can be achieved by offloading time-consuming tasks to non-interrupt contexts and using efficient data structures and algorithms within the ISR.

Interrupt synchronization mechanisms play a crucial role in reducing interrupt latency in RTOS environments. By properly synchronizing interrupts and avoiding conflicts, the system can minimize the time it takes to service interrupts and improve overall system performance. Techniques such as disabling interrupts during critical sections, using semaphores and mutexes for synchronization, and implementing interrupt-safe data structures can help reduce interrupt latency in the system.

It is also important to consider the hardware architecture and platformspecific characteristics when implementing interrupt latency reduction strategies. Different hardware platforms may have different interrupt handling mechanisms and latency characteristics, so it is important to tailor the strategies to the specific hardware environment. By understanding the hardware architecture and platform-specific characteristics, embedded engineers can optimize interrupt latency and improve system performance in real-time applications.

In conclusion, implementing interrupt latency reduction strategies is essential for optimizing real-time performance in embedded systems. By prioritizing critical interrupts, minimizing ISR execution time, using proper interrupt synchronization mechanisms, and considering hardware-specific characteristics, embedded engineers can effectively reduce interrupt latency and improve system responsiveness in RTOS environments. By following these best practices and techniques, engineers can ensure that their embedded systems meet the demands of time-critical applications.

#### Testing and Validating Interrupt Synchronization Mechanisms

In the world of real-time operating systems (RTOS), reducing interrupt latency is a critical goal for embedded engineers. One key aspect of achieving low interrupt latency is the implementation of effective interrupt synchronization mechanisms. In this subchapter, we will delve into the importance of testing and validating these mechanisms to ensure they meet the requirements of real-time applications.

Testing interrupt synchronization mechanisms is crucial to verify that they function as intended and do not introduce additional latency. Engineers should design test cases that simulate various interrupt scenarios and measure the resulting latency. By conducting thorough testing, engineers can identify any potential bottlenecks or issues that may impact the system's performance.

Validation is another essential step in ensuring the reliability of interrupt synchronization mechanisms. Engineers should validate the mechanisms through both simulation and real-world testing to confirm that they meet the timing requirements of the application. Validation also helps identify any corner cases or edge conditions that may lead to unpredictable behavior.

One common approach to testing interrupt synchronization mechanisms is to use a combination of hardware-in-the-loop (HIL) testing and software-inthe-loop (SIL) testing. HIL testing involves connecting the RTOS to physical hardware to simulate real-world conditions, while SIL testing focuses on testing the software independently of the hardware. By combining these two methods, engineers can thoroughly validate the interrupt synchronization mechanisms across different environments. In conclusion, testing and validating interrupt synchronization mechanisms is crucial for ensuring low interrupt latency in real-time operating systems. By following a systematic approach to testing and validation, embedded engineers can identify and address any potential issues before they impact the performance of the system. Ultimately, a well-tested and validated interrupt synchronization mechanism is essential for meeting the stringent timing requirements of real-time applications.

## **Chapter 6: Conclusion and Future Trends**

#### **Summary of Key Points**

In this subchapter, we have discussed the key points related to optimizing interrupt latency in real-time operating systems (RTOS) for embedded engineers. Interrupt latency reduction strategies are crucial for ensuring timely response to critical events in real-time systems. By minimizing interrupt latency, embedded engineers can improve the overall performance and reliability of their systems.

One key point to consider is the importance of understanding the sources of interrupt latency in RTOS. By identifying the factors contributing to latency, engineers can develop targeted strategies for reducing delays in interrupt handling. Common sources of interrupt latency include context switching overhead, interrupt nesting, and interrupt priority inversion.

Another key point is the significance of implementing interrupt synchronization mechanisms in RTOS. Synchronization mechanisms such as semaphores, mutexes, and event flags are essential for managing shared resources and preventing race conditions in interrupt-driven systems. By carefully designing and implementing synchronization mechanisms, engineers can ensure mutual exclusion and proper synchronization of tasks and interrupts.

Furthermore, we have highlighted the benefits of utilizing interrupt preemption and prioritization techniques in RTOS. By assigning priorities to interrupts and preempting lower-priority tasks, engineers can minimize interrupt latency and ensure timely response to high-priority events. Additionally, implementing interrupt-driven scheduling policies can help optimize system performance and improve overall responsiveness. Overall, optimizing interrupt latency in real-time operating systems requires a comprehensive understanding of the factors affecting interrupt handling and the implementation of effective strategies for reducing latency. By applying the key points discussed in this subchapter, embedded engineers can enhance the reliability, responsiveness, and performance of their realtime systems.

#### **Emerging Technologies in Interrupt Latency Optimization**

In the ever-evolving world of real-time operating systems (RTOS), interrupt latency optimization is a crucial aspect that embedded engineers must constantly strive to improve. As technology advances, so too must our strategies for reducing interrupt latency in order to meet the demands of increasingly complex embedded systems. One area of focus in this pursuit is the exploration of emerging technologies that offer new opportunities for interrupt latency optimization.

One such technology that shows promise in interrupt latency reduction strategies is the use of hardware accelerators. By offloading certain tasks to specialized hardware units, engineers can significantly reduce the time it takes to process interrupts, thereby minimizing latency. Hardware accelerators offer a level of efficiency and speed that is difficult to achieve through software alone, making them a valuable tool for optimizing interrupt latency in RTOS's.

Another emerging technology that holds potential for interrupt latency optimization is the use of multicore processors. By distributing interrupt processing across multiple cores, engineers can parallelize tasks and reduce latency without compromising system performance. Multicore processors offer scalability and flexibility, allowing for more efficient handling of interrupts in complex embedded systems. In addition to hardware-based solutions, emerging technologies in interrupt synchronization mechanisms are also worth exploring. Synchronization mechanisms play a critical role in managing the order and timing of interrupts, ensuring that critical tasks are executed in a timely manner. By leveraging emerging synchronization techniques, engineers can further optimize interrupt latency in RTOS's and improve overall system responsiveness.

Overall, the field of interrupt latency optimization in real-time operating systems is constantly evolving, driven by advancements in technology and the increasing demands of embedded systems. Embedded engineers must stay abreast of emerging technologies and techniques in order to effectively reduce interrupt latency and enhance system performance. By embracing new tools and strategies, engineers can continue to push the boundaries of interrupt latency optimization and meet the challenges of today's complex embedded systems.

#### **Final Thoughts for Embedded Engineers**

In conclusion, it is important for embedded engineers to understand the significance of reducing interrupt latency in real-time operating systems (RTOS). By implementing effective strategies to minimize interrupt latency, engineers can improve the overall performance and responsiveness of their embedded systems. This can lead to better user experiences and increased efficiency in critical applications.

Furthermore, engineers should also pay close attention to interrupt synchronization mechanisms in RTOS. By properly synchronizing interrupts, engineers can prevent conflicts and ensure that critical tasks are executed in a timely manner. This can help to avoid system crashes and data corruption, ultimately increasing the reliability and stability of the embedded system. It is crucial for embedded engineers to stay up-to-date with the latest developments in interrupt latency reduction strategies and interrupt synchronization mechanisms in RTOS. By continuously learning and adapting to new technologies and techniques, engineers can optimize the performance of their embedded systems and stay ahead of the competition.

In conclusion, optimizing interrupt latency in real-time operating systems is a complex and challenging task that requires careful planning and attention to detail. However, by following the guidelines and best practices outlined in this book, embedded engineers can effectively reduce interrupt latency and improve the overall performance of their systems. By staying informed and proactive, engineers can ensure that their embedded systems meet the highest standards of reliability and efficiency.

## **Appendix A: Glossary of Terms**

As embedded engineers delve into the world of real-time operating systems (RTOS), it becomes crucial to have a solid understanding of the terminology commonly used in this field. This glossary aims to provide a comprehensive list of terms related to interrupt latency reduction strategies and interrupt synchronization mechanisms in RTOS's.

**1. Interrupt Latency**: The time interval between the occurrence of an interrupt and the initiation of the corresponding interrupt service routine (ISR). Minimizing interrupt latency is essential for meeting real-time deadlines in embedded systems.

**2. Interrupt Service Routine (ISR)**: A function that is executed in response to an interrupt request. ISRs are responsible for handling the interrupt and performing any necessary actions, such as updating data structures or responding to external events.

**3. Interrupt Priority**: A numerical value assigned to each interrupt source to determine its priority level. Higher priority interrupts are serviced before lower priority interrupts, helping to reduce overall interrupt latency in the system.

**4. Interrupt Nesting**: The ability of an RTOS to handle multiple interrupts simultaneously by nesting ISR execution. Proper interrupt nesting management is crucial for ensuring the timely processing of critical interrupts without introducing unnecessary delays.

**5. Interrupt Synchronization**: Techniques used to coordinate the execution of multiple ISRs and prevent race conditions in shared resources. Common synchronization mechanisms include semaphores, mutexes, and event flags, which help ensure the integrity of data accessed by concurrent interrupt handlers.

In conclusion, a solid grasp of the terminology related to interrupt latency reduction strategies and interrupt synchronization mechanisms is essential for embedded engineers working with real-time operating systems. By familiarizing themselves with these concepts, engineers can effectively optimize interrupt handling in their systems, ensuring timely and deterministic behavior in critical applications. This glossary serves as a valuable reference tool for navigating the complexities of RTOS development and implementation.

# **Appendix B: Additional Resources for Further Reading**

For embedded engineers seeking to optimize interrupt latency in real-time operating systems (RTOS), there are a variety of resources available for further reading on interrupt latency reduction strategies and interrupt synchronization mechanisms. This appendix provides a curated list of recommended books, articles, and online resources that delve deeper into these topics.

#### 1. <u>"Real-Time Systems Design and Analysis" by Phillip A. Laplante</u>

This comprehensive book offers a thorough exploration of real-time systems design principles and techniques, including a detailed discussion on interrupt latency reduction strategies. It provides valuable insights into the impact of interrupt handling on system performance and offers practical guidance on how to minimize interrupt latency in RTOS environments.

#### 2. <u>"Embedded Systems: Real-Time Interfacing to ARM Cortex-M</u> <u>Microcontrollers" by Jonathan W. Valvano</u>

This book is a must-read for embedded engineers working with ARM Cortex-M microcontrollers and seeking to optimize interrupt latency. It covers a wide range of topics related to real-time interfacing, including interrupt handling and synchronization mechanisms in RTOS environments.

# **3.** "Operating Systems: Internals and Design Principles" by William Stallings

For a more in-depth understanding of interrupt synchronization mechanisms in RTOS's, this book is an excellent resource. It explores the inner workings of operating systems, including the role of interrupts in system operation and the various synchronization techniques used to manage interrupt latency.

# 4. "RTOS Fundamentals: Interrupt Handling in Real Time Operating System" by EmbeddedCraft

This online resource provides a detailed overview of interrupt handling in RTOS environments, with a focus on practical strategies for reducing interrupt latency. It covers key concepts such as interrupt priorities, interrupt nesting, and interrupt service routines, offering valuable insights for embedded engineers looking to optimize system performance.

#### 5. Embedded Systems Blogs and Forums

In addition to books and articles, there are numerous online blogs and forums dedicated to embedded systems design and development. Websites such as **Embedded.com**, **EEVblog**, and **Stack Exchange** provide a wealth of information on interrupt latency reduction strategies and interrupt synchronization mechanisms in RTOS's, as well as a platform for networking with other embedded engineers and sharing best practices.

By exploring these additional resources, embedded engineers can deepen their understanding of interrupt latency optimization in real-time operating systems and gain valuable insights into the latest trends and best practices in the field. Whether you are a seasoned professional or a newcomer to the world of embedded systems, there is always more to learn and discover in the quest for optimal system performance.

# **About The Author**

Lance Harvie Bsc (Hons), with a rich background in both engineering and technical recruitment, bridges the unique gap between technical deep expertise and talent acquisition. Educated in Microelectronics and Information Processing at the University of he transitioned Brighton, UK, from an embedded engineer to an influential figure in technical recruitment, founding and leading

firms globally. Harvie's extensive international experience and leadership roles, from CEO to COO, underscore his versatile capabilities in shaping the tech recruitment landscape. Beyond his business achievements, Harvie enriches the embedded systems community through insightful articles, sharing his profound knowledge and promoting industry growth. His dual focus on technical mastery and recruitment innovation marks him as a distinguished professional in his field.

#### **Connect With Us!**

RunTime Recruitment 2024